Altera Transceiver Signal Integrity Development Kit, Stratix V GX Edition User Manual

Page 42

2–34

Chapter 2: Board Components

Components and Interfaces

Transceiver Signal Integrity Development Kit

July 2012

Altera Corporation

Stratix V GX Edition Reference Manual

73

ENET_LED_LINK1000

2.5-V

—

1000-Mb link LED

69

ENET_LED_RX

2.5-V

—

RX data active LED

68

ENET_LED_TX

2.5-V

—

TX data active LED

28

ENET_RSTN

2.5-V

AT6

Device reset

75

ENET_SGMII_RX_N

2.5-V

AJ15

SGMII receive

77

ENET_SGMII_RX_P

2.5-V

AH15

SGMII receive

81

ENET_SGMII_TX_N

2.5-V

AL15

SGMII transmit

82

ENET_SGMII_TX_P

2.5-V

AK15

SGMII transmit

55

ENET_XTAL_25MHZ

2.5-V

—

25-MHz clock

8

GTXCLK

2.5-V

AE15

Ethernet transmit clock

25

MDC

2.5-V

AB16

Management bus data clock

31

MDI_N0

2.5-V

—

Management bus data

34

MDI_N1

2.5-V

—

Management bus data

41

MDI_N2

2.5-V

—

Management bus data

43

MDI_N3

2.5-V

—

Management bus data

29

MDI_P0

2.5-V

—

Management bus data

33

MDI_P1

2.5-V

—

Management bus data

39

MDI_P2

2.5-V

—

Management bus data

42

MDI_P3

2.5-V

—

Management bus data

24

MDIO

2.5-V

AC16

Management bus data input/output

2

RXCLK

2.5-V

AH16

SGMII receive clock

95

RXD0

2.5-V

AG17

SGMII receive data

92

RXD1

2.5-V

AD15

SGMII receive data

93

RXD2

2.5-V

AE16

SGMII receive data

91

RXD3

2.5-V

AB15

SGMII receive data

94

RXDV

2.5-V

AF17

SGMII receive data valid

11

TXD0

2.5-V

AK17

SGMII transmit data

12

TXD1

2.5-V

AL17

SGMII transmit data

14

TXD2

2.5-V

AJ16

SGMII transmit data

16

TXD3

2.5-V

AJ17

SGMII transmit data

9

TXEN

2.5-V

AF16

SGMII transmit enable

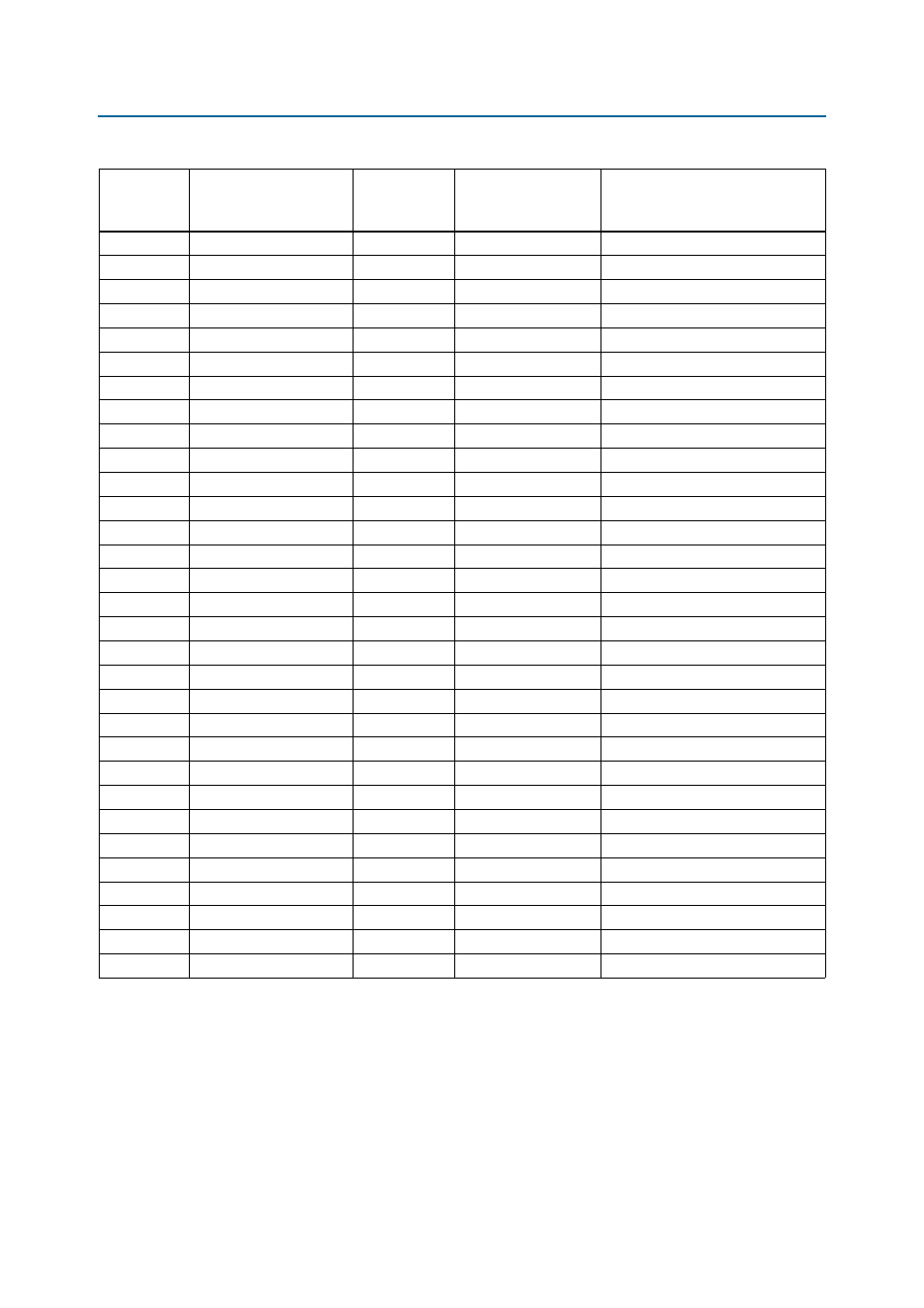

Table 2–32. Ethernet PHY Pin Assignments, Signal Names and Functions

Board

Reference

(U22)

Schematic Signal Name

I/O Standard

Stratix V GX Device

Pin Number

Description