Hsmc, Hsmc –37 – Altera Arria V GT FPGA Development Board User Manual

Page 47

Chapter 2: Board Components

2–37

Components and Interfaces

December 2014

Altera Corporation

Arria V GT FPGA Development Board

Reference Manual

HSMC

The development board contains two HSMC interfaces—port A on device 1 and

port B on device 2. HSMC port A and port B interfaces support both single-ended and

differential signaling. This physical interface provides eight channels of

6.5536 Gbps-capable transceivers for the GT version of this board. The HSMC

interface also supports a full SPI4.2 interface (17 LVDS channels), three input and

output clocks, JTAG and SMB signals, as well as power for compatible HSMC cards.

The LVDS channels can be used for CMOS signaling as well as LVDS.

1

The HSMC is an Altera-developed open specification, which allows you to expand

the functionality of the development board through the addition of daughtercards

(HSMCs).

30

ENET_RSET

—

2.5-V CMOS

Bias voltage for the Ethernet PHY. This pin

connects to ground through a 4.99-K

resistor.

2

ENET_RX_CLK

AK7

2.5-V CMOS

RGMII receive clock

95

ENET_RX_D0

AU17

2.5-V CMOS

RGMII receive data

92

ENET_RX_D1

AT17

2.5-V CMOS

RGMII receive data

93

ENET_RX_D2

AW16

2.5-V CMOS

RGMII receive data

91

ENET_RX_D3

AH18

2.5-V CMOS

RGMII receive data

94

ENET_RX_DV

AW17

2.5-V CMOS

RGMII receive data valid

75

ENET_RX_N

AK19

2.5-V CMOS

RGMII receive channel

77

ENET_RX_P

AL19

2.5-V CMOS

RGMII receive channel

11

ENET_TX_D0

AT19

2.5-V CMOS

RGMII transmit data

12

ENET_TX_D1

AU18

2.5-V CMOS

RGMII transmit data

14

ENET_TX_D2

AH19

2.5-V CMOS

RGMII transmit data

16

ENET_TX_D3

AG19

2.5-V CMOS

RGMII transmit data

9

ENET_TX_EN

AP19

2.5-V CMOS

RGMII transmit enable

81

ENET_TX_N

AE19

2.5-V CMOS

RGMII transmit channel

82

ENET_TX_P

AF19

2.5-V CMOS

RGMII transmit channel

55

ENET_XTAL_25MHZ

—

2.5-V CMOS

25-MHz clock

29

MDI_P0

—

2.5-V CMOS

Media dependent interface 0

31

MDI_N0

—

2.5-V CMOS

Media dependent interface 0

33

MDI_P1

—

2.5-V CMOS

Media dependent interface 1

34

MDI_N1

—

2.5-V CMOS

Media dependent interface 1

39

MDI_P2

—

2.5-V CMOS

Media dependent interface 2

41

MDI_N2

—

2.5-V CMOS

Media dependent interface 2

42

MDI_P3

—

2.5-V CMOS

Media dependent interface 3

43

MDI_N3

—

2.5-V CMOS

Media dependent interface 3

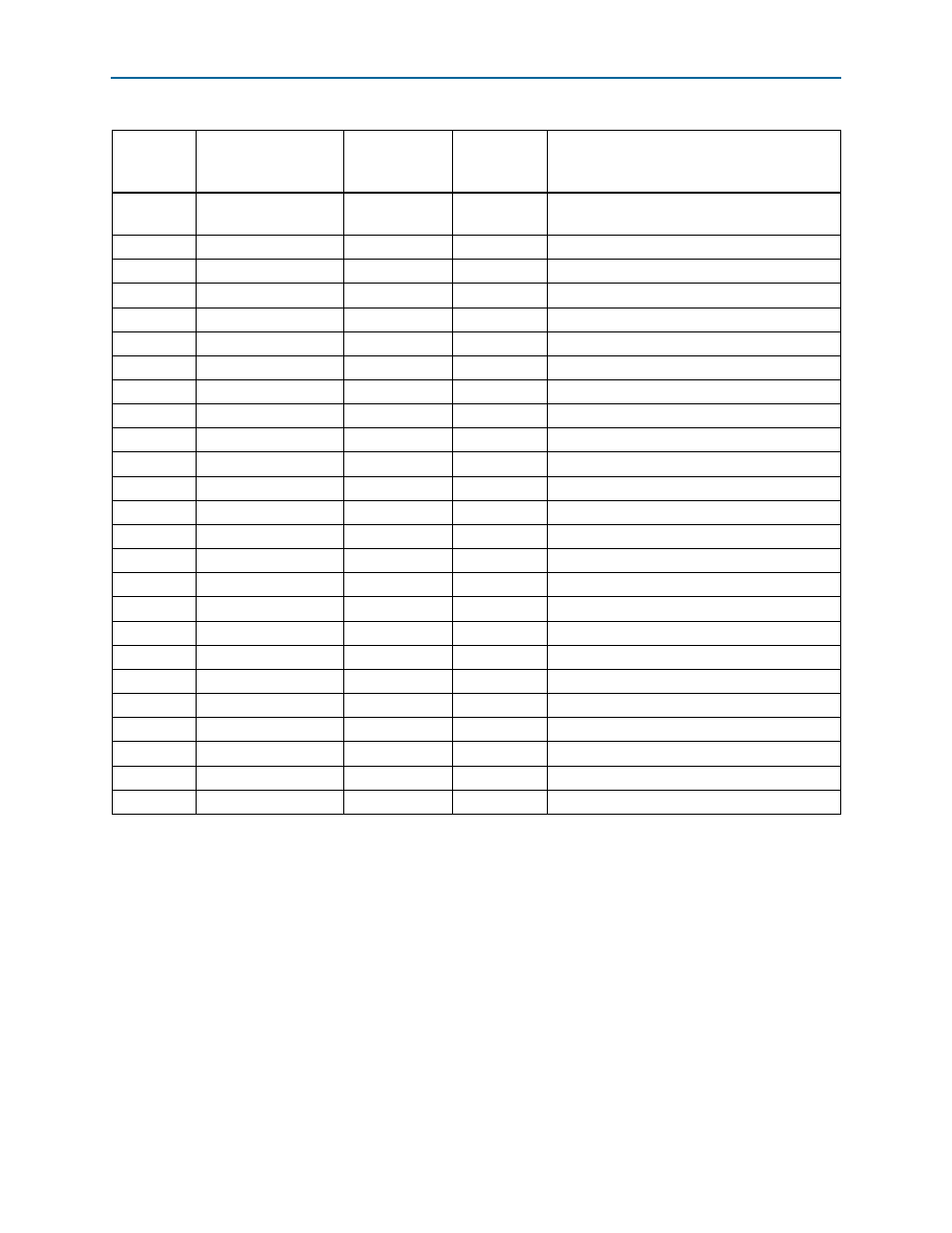

Table 2–25. Ethernet PHY Pin Assignments, Signal Names and Functions (Part 2 of 2)

Board

Reference

(U14)

Schematic Signal

Name

Arria V GT FPGA

Pin Number

I/O Standard

Description