Zilog Z16C30 User Manual

Page 146

7-18

Z16C30 USC

®

U

SER

'

S

M

ANUAL

UM97USC0100

Z

ILOG

7.11.2 Receive Data Interrupts

(Continued)

7.11.3 Transmit Status Interrupt Sources

and IA Bits

The interrupt logic can set the

Transmit Status IP

bit in

response to any of six interrupt sources. Software can read

the status of each source in the LSByte of the Transmit

Command/Status Register (TCSR), which is shown in

Figure 7-12. The following descriptions of the TCSR bits

are similar to those in the 'Detailed Status in the TCSR'

section of Chapter 5.

PreSent

The interrupt logic can set the TS IP bit

when this bit (TCSR7) goes from a 0 to

a 1, because the transmitter has fin-

ished sending the “Preamble” se-

lected in the Channel Control Regis-

ter (CCR11-8) in a synchronous mode.

IdleSent

The interrupt logic can set the TS IP bit

when this bit (TCSR6) goes from a 0 to

a 1, because the transmitter has sent

the idle line state selected by the

TxIdle field (TCSR10-8). If TxIdle and

TxMode specify the condition as Flags

or Syncs, this bit can be set for each

one sent. Otherwise, for bit-oriented

Idle conditions, it’s set only after the

first bit is sent.

AbortSent

The interrupt logic can set the TS IP bit

in HDLC/SDLC mode, when this bit

(TCSR5) goes from 0 to 1 because the

transmitter has sent an Abort charac-

ter.

EOF/EOM Sent

The interrupt logic can set the TS IP bit

in a synchronous mode, when this bit

(TCSR4) goes from 0 to 1 because the

transmitter has sent the closing Flag

or Sync character at the end of a

message or frame.

CRCSent

The interrupt logic can set the TS IP bit

in a sync mode, when this bit (TCSR3)

goes from 0 to 1 because the trans-

mitter has sent the CRC sequence

just before the end of a message or

frame.

TxUnder

The interrupt logic can set the TS IP bit

when this bit (TCSR1) goes from 0 to

1, because the transmitter needed a

character from the TxFIFO but it was

empty.

Once one of these TCSR bits is 1, it must be cleared to 0

by writing a 1 to that bit position in TCSR.

In order to ensure that future interrupts are requested

properly when more than one Transmit Status condition is

Armed in the TICR, a Transmit Status interrupt service

routine must clear all of the IA bits in the TICR and then set

the desired ones again, after it has cleared the TS IP bit and

the TCSR bits that it has serviced.

Each of these six sources has a separate

Interrupt Arm

(IA)

bit in the LSByte of the Transmit Interrupt Control

Register (TICR). Figure 7-13 shows the TICR. If an IA bit is

1, the interrupt logic sets the Transmit Status IP bit when

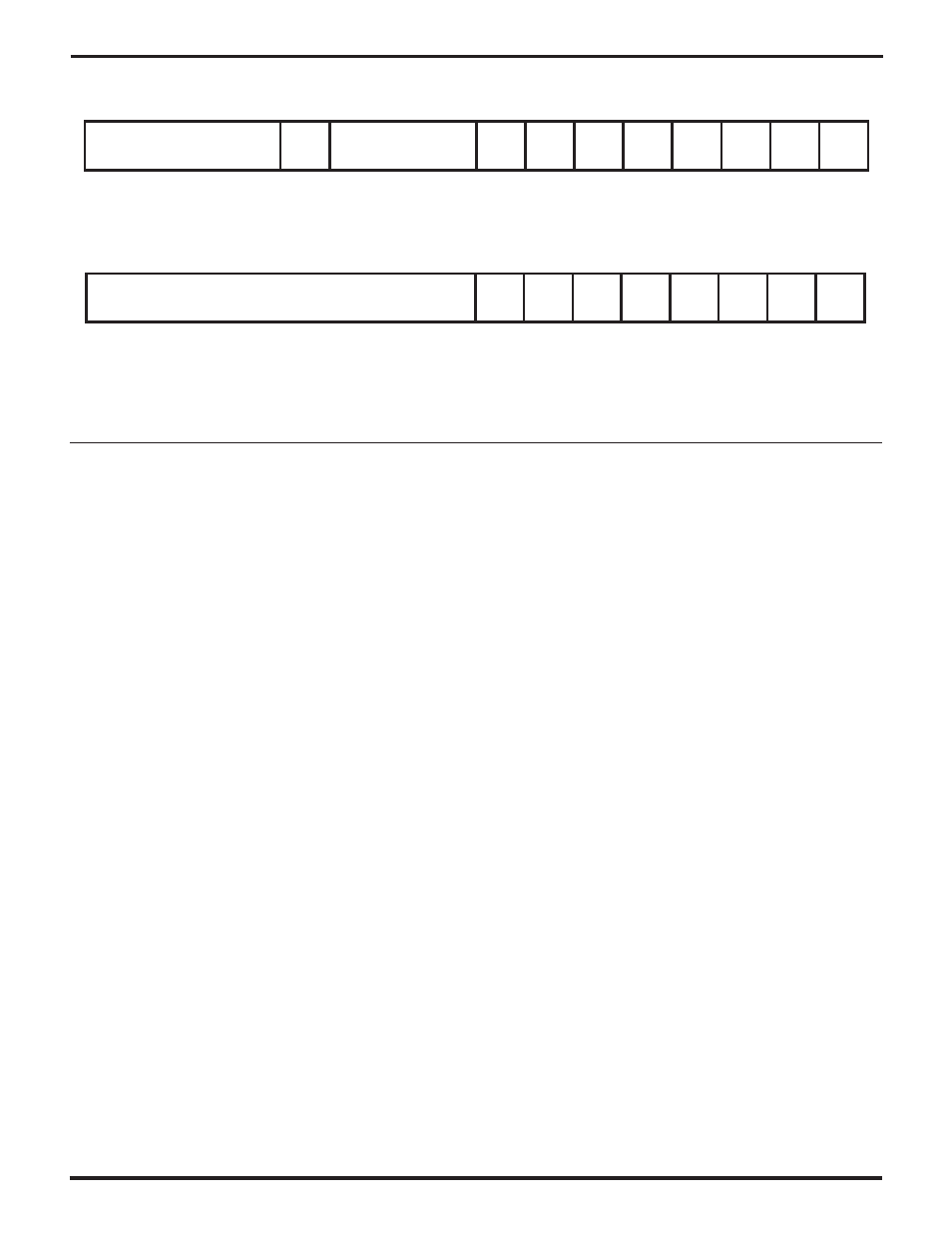

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

Pre

Sent IA

Idle

Sent

IA

Abort

Sent

IA

EOF/

EOM

Sent IA

CRC

Sent

IA

Wait2

Send

Tx

Under

IA

TC1R

Sel

"TxFIFOStatus" if last TCSR 15-12 command 4-7 was 5

"Tx Int level" if last RCSR 15-12 command 4-7 was 6

"Tx DMA Req level" If last TCSR 15-12 command 4-7 was 7

Figure 7-13. The Transmit Interrupt Control Register (TICR)

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

TCmd

Rsrvd

Txidle

Pre

Sent

Idle

Sent

Abort

Sent

EOF/

EOM

Sent

CRC

Sent

All

Sent

Tx

Under

Tx

Empty

Figure 7-12. The Transmit Command/Status Register (TCSR)

UM009402-0201