Lddr – Zilog Z08470 User Manual

Page 146

Z80 Instruction Set

UM008007-0715

134

Z80 CPU

User Manual

LDDR

Operation

(DE) ← (HL), DE ← D ← 1, HL ← HL– 1, BC ← BC – 1

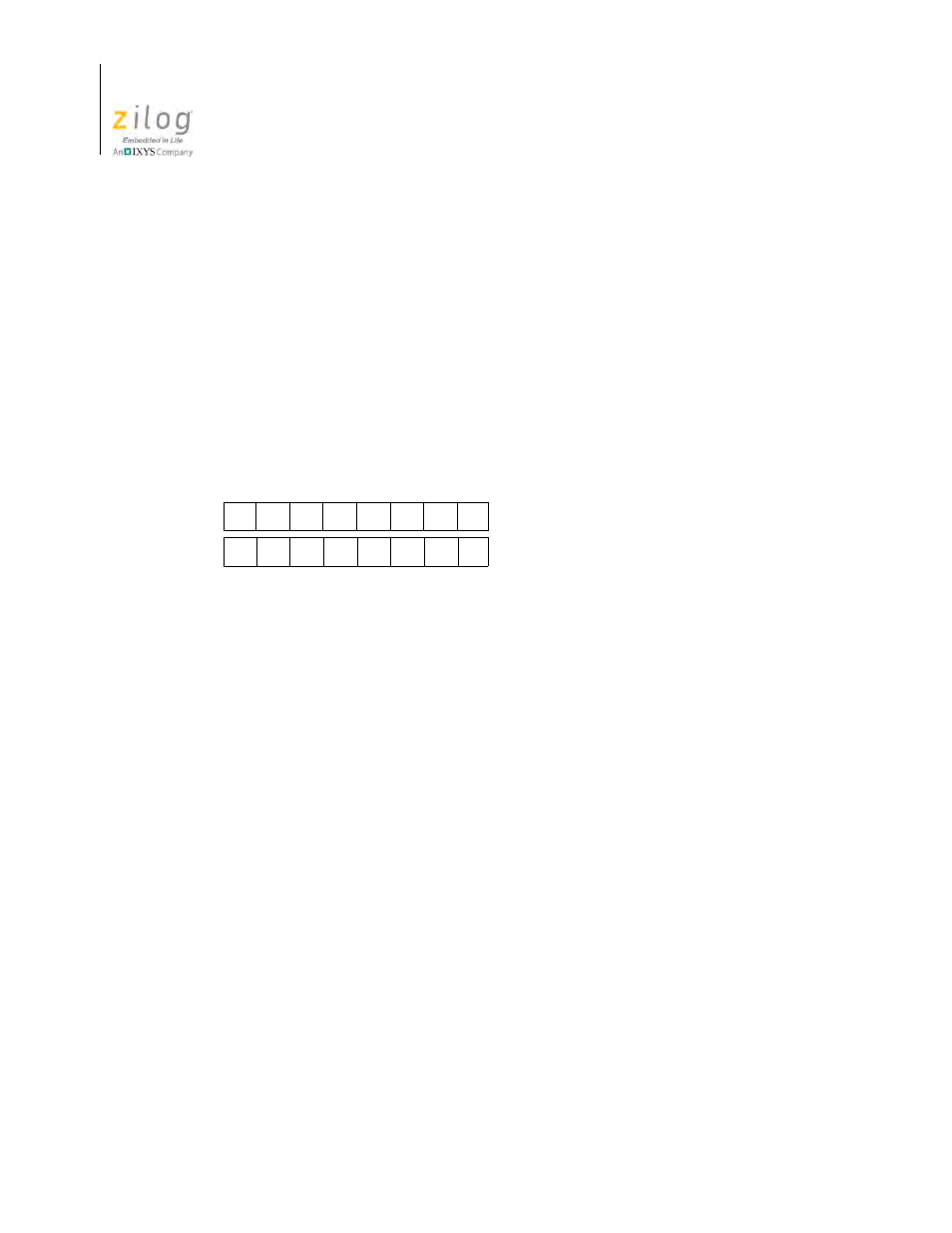

Op Code

LDDR

Operands

None.

Description

This 2-byte instruction transfers a byte of data from the memory location addressed by the

contents of the HL register pair to the memory location addressed by the contents of the

DE register pair. Then both of these registers, and the BC (Byte Counter), are decre-

mented. If decrementing causes BC to go to 0, the instruction is terminated. If BC is not 0,

the program counter is decremented by two and the instruction is repeated. Interrupts are

recognized and two refresh cycles execute after each data transfer.

When the BC is set to 0, prior to instruction execution, the instruction loops through

64 KB.

For BC ≠ 0:

For BC = 0:

M Cycles

T States

4 MHz E.T.

5

21 (4, 4, 3, 5, 5)

5.25

M Cycles

T States

4 MHz E.T.

4

16 (4, 4, 3, 5)

4.00

1

1

0

0

1

1

1

1

ED

1

0

1

0

0

0

1

1

B8