Power-down release cycle, Figure 13. power-down release cycle, #1 of 3, Figure 14. power-down release cycle, #2 of 3 – Zilog Z08470 User Manual

Page 28

Architectural Overview

UM008007-0715

16

Z80 CPU

User Manual

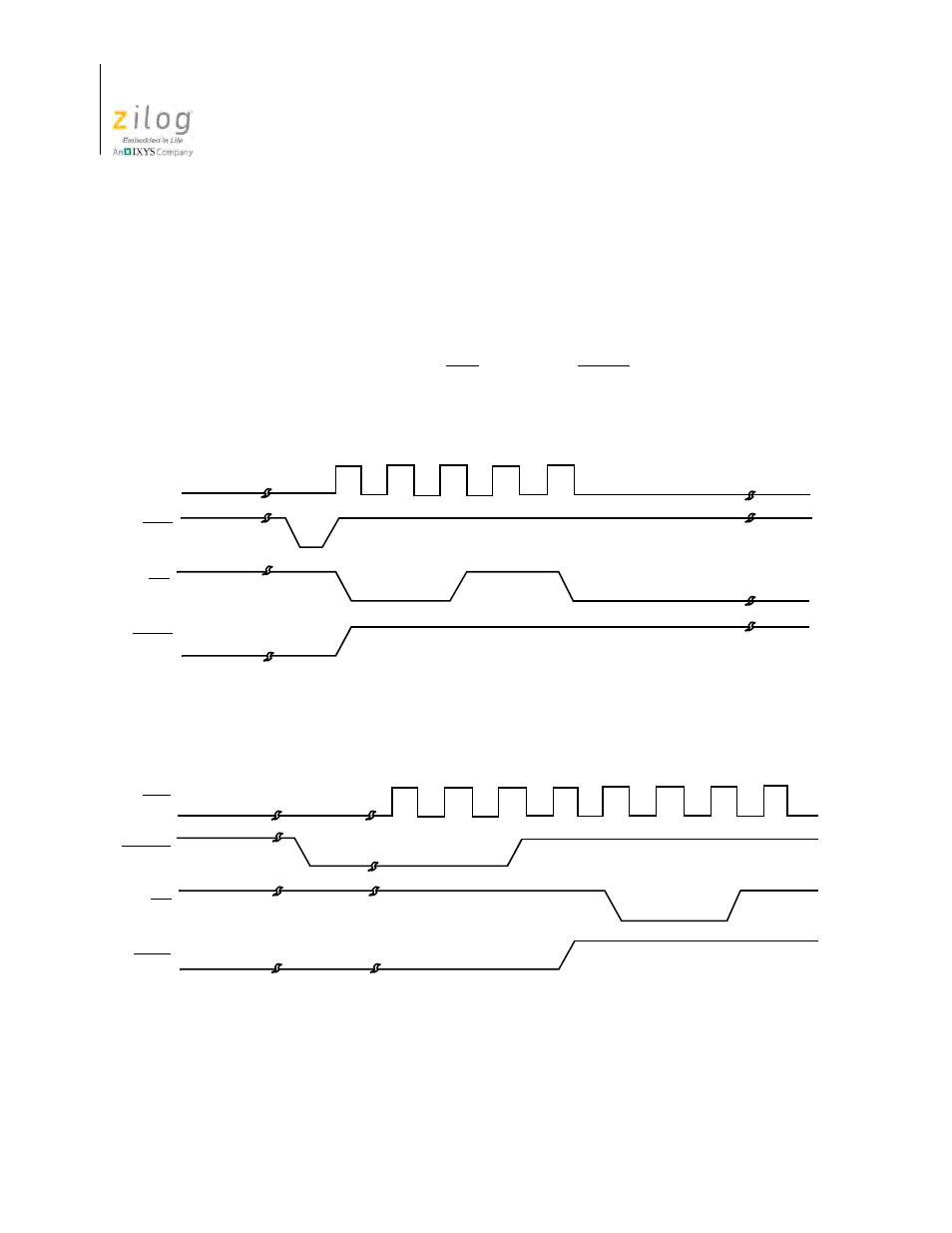

Power-Down Release Cycle

The system clock must be supplied to the Z80 CPU to release the power-down state. When

the system clock is supplied to the CLK input, the Z80 CPU restarts operations from the

point at which the power-down state was implemented. The timing diagrams for the

release from power-down mode are featured in Figures 13 through 15. When the HALT

instruction is executed to enter the power-down state, the Z80 CPU also enters the HALT

state. An interrupt signal (either NMI or ANT) or a RESET signal must be applied to the

CPU after the system clock is supplied to release the power-down state.

Figure 13. Power-Down Release Cycle, #1 of 3

Figure 14. Power-Down Release Cycle, #2 of 3

CLK

HALT

T1

T2

T3

T1

M1

T4

NMI

CLK

HALT

T1

T2

T3

M1

T4

RESET