Table "telecom clocking interrupt status, Is als, Table "telecom clocking – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 338: Cpld and fpga

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

338

IPMC Interrupt Register

Telecom Clocking Interrupt Registers

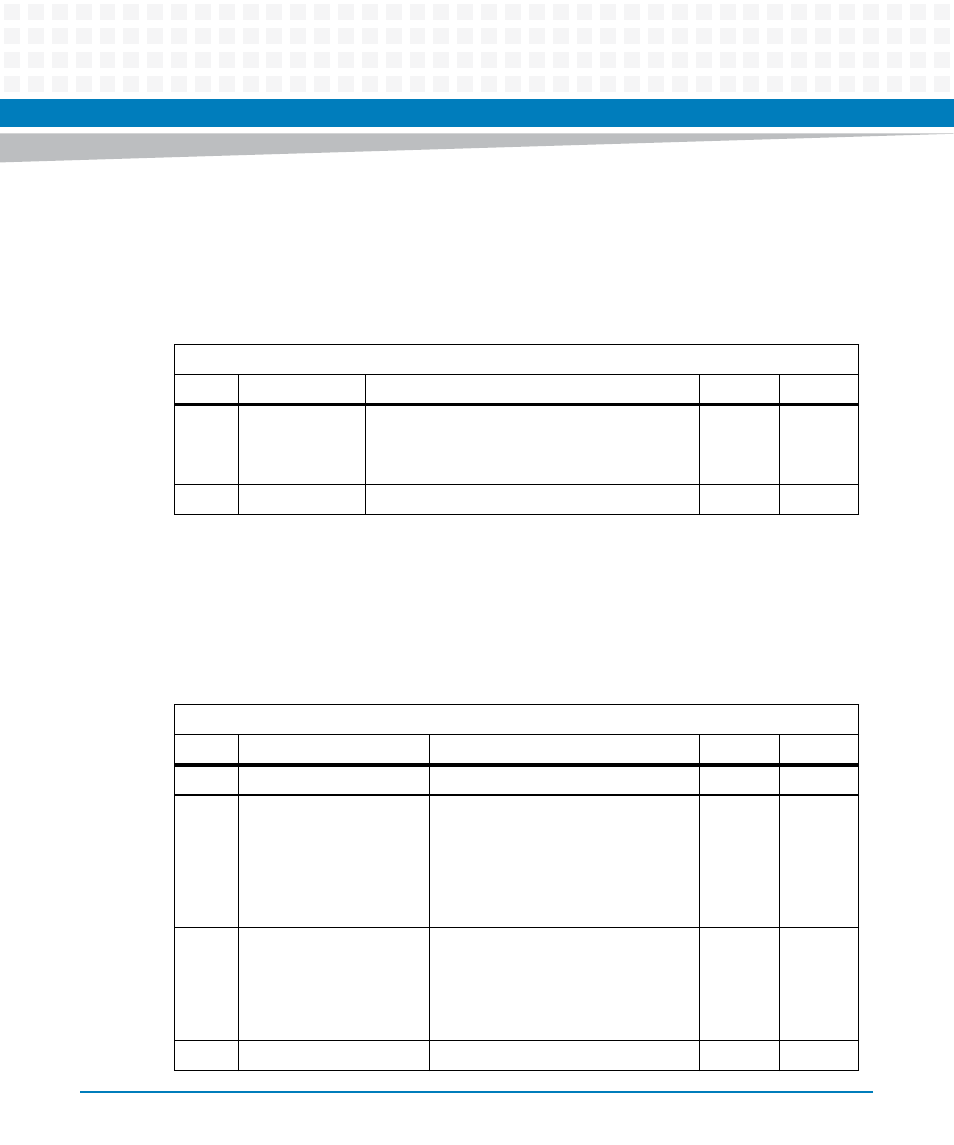

Table 8-146 IPMC KCS Interrupt Enable Register

Address: 0x9E - 0x9F

Bit Interrupt

Name

Description

Default

Access

0

KCS_IRQ

KCS Interrupt enable:

0: Disabled

1:Enabled

0

SPP: r/w

15:1

-

Reserved

0

r

Table 8-147 Telecom Clocking Interrupt Status Register

Address: 0xA0 - 0xA1

Bit Interrupt

Name

Description

Default

Access

0

ACS8520_IRQ

Interrupt from device ACS8520

0

SPP: r

1

CLK_MONITOR_FINISHE

D

Interrupt from Telecom Clock

supervision. At least one

measurement for the supervised

clocks has finished.

See Table 89 Telecom Clock Monitor

Status Register

0

SPP: r

2

CLK_MONITOR_OUT_OF

_RANGE

Interrupt from Telecom Clock

supervision. At least one supervised

clock is out of range.

See Table 90 Telecom Clock Monitor

Out of Range Register.

0

SPP: r

15:2

-

Reserved

0

r