Control header, Config (jp3pins 1 & 2), Ontrol – Sundance SMT401 User Manual

Page 10: Eader

Released

Page 10 of 21

SMT401 PMC TIM Carrier User Guide

Document Name:

SMT401 User Guide V1.2.doc

Issue : 02

Rev.: 1.11

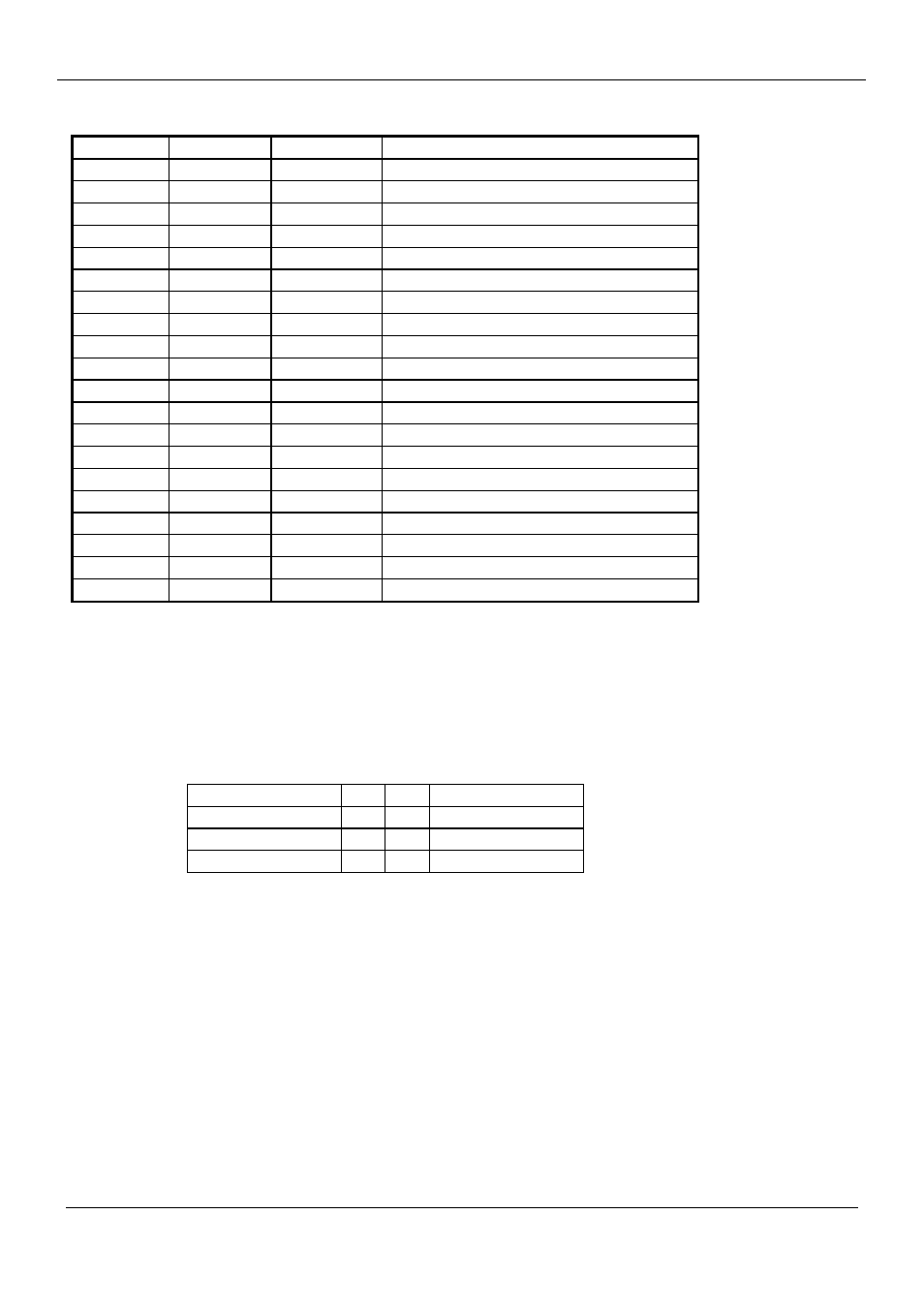

Pin Signal

Direction

Description

1

TDI

OUT

JTAG data out

2 GND

3

TDO

IN

JTAG data in

4 GND

5

TMS

OUT

JTAG Test mode select

6 GND

7

TCK

OUT

JTAG clock 10MHz

8 GND

9

TCK_RET

IN

JTAG clock return

10 GND

11 -TRST

OUT JTAG

Reset

12 GND

13

-RESET

OUT

Board Reset out

14

PD

IN

Presence detect when pulled high

15

-DETECT

OUT

Detect external JTAG controller when grounded

16 CONFIG

OPEN

COLL

Global

open collector C4x CONFIG

17 EMU0

IN Buffered

EMU0

output

18 EMU1

IN Buffered

EMU1

output

19 SPARE1

20 SPARE2

Table 2 JTAG Master Port (Output)

3.3

Control Header

An eight pin header, JP3, provides reset, the #CONFIG signal, and a jumper

which dictates when used under Parallel C whether the ADM-C4X is to act as

a link engine, or as an attached processor:

GND

1

2

#CONFIG

GND

3

4

#RESET_IN

GND

5

6

#BUSRESET

MODE (see below)

7 8

MODE (see below)

3.3.1

#CONFIG (JP3pins 1 & 2)

#CONFIG is an active-low, open-drain output from the SMT401. If there is a

TIM fitted to the SMT401 #CONFIG can be driven low, but never driven high,

by the TIM.

Pin 1 is provided simply as an associated ground signal for #CONFIG.

Product Name:

SMT401

Revision Date:

07 December 2004

Author:

Mark I. Cartlidge (Updated by SM, added JTAG slave section)

Original Date:

12 May 1999