Altera MAX 10 Embedded Memory User Manual

Page 58

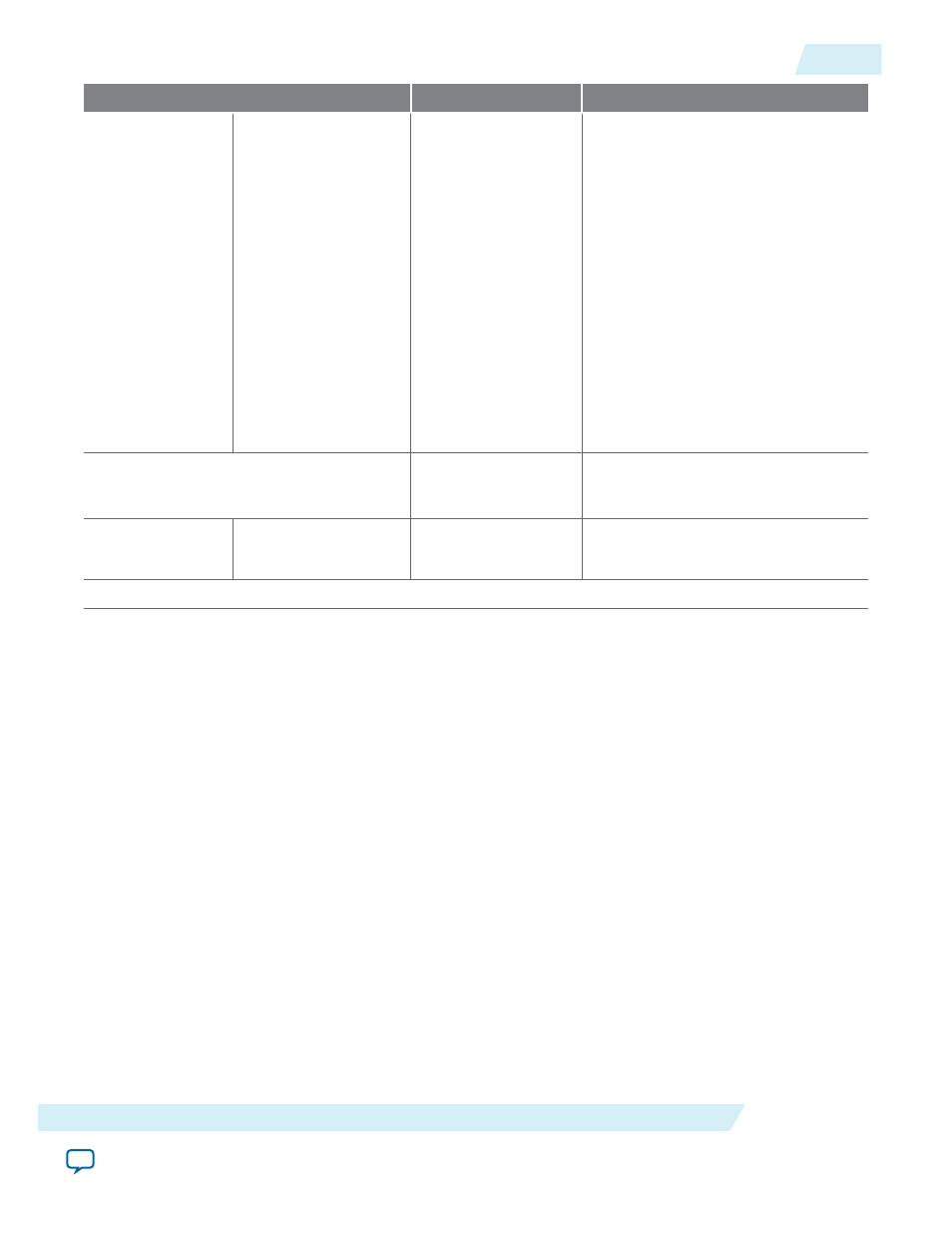

Option

Legal Values

Description

More Options

• Clock enable options

• Use clock enable

for port A input

registers

• Use clock enable

for port A output

registers

• Address options

• Create an

‘addressstall_a’

input port.

• Create an

‘addressstall_b’

input port.

•

On/Off

• Clock enable options—Clock

enable for port B input and

output registers are turned on by

default. You only need to specify

whether to use clock enable for

port A input and output

registers.

• Address options—Specifies

whether to create clock enables

for address registers. You can

create these ports to act as an

extra active low clock enable

input for the address registers.

Create an ‘aclr’ asynchronous clear for the

registered ports.

On/Off

Specifies whether to create an

asynchronous clear port for the

registered ports.

More Options

• ‘q_a’ port

• ‘q_b’ port

On/Off

Specifies whether the ‘q_a’, and ‘q_b’

ports are cleared by the aclr port.

Parameter Settings: Mem Init

UG-M10MEMORY

2015.05.04

ROM:2-Port IP Core Parameters For MAX 10 Devices

7-7

ROM: 2-PORT IP Core References

Altera Corporation