Altera PHYLite User Manual

Page 55

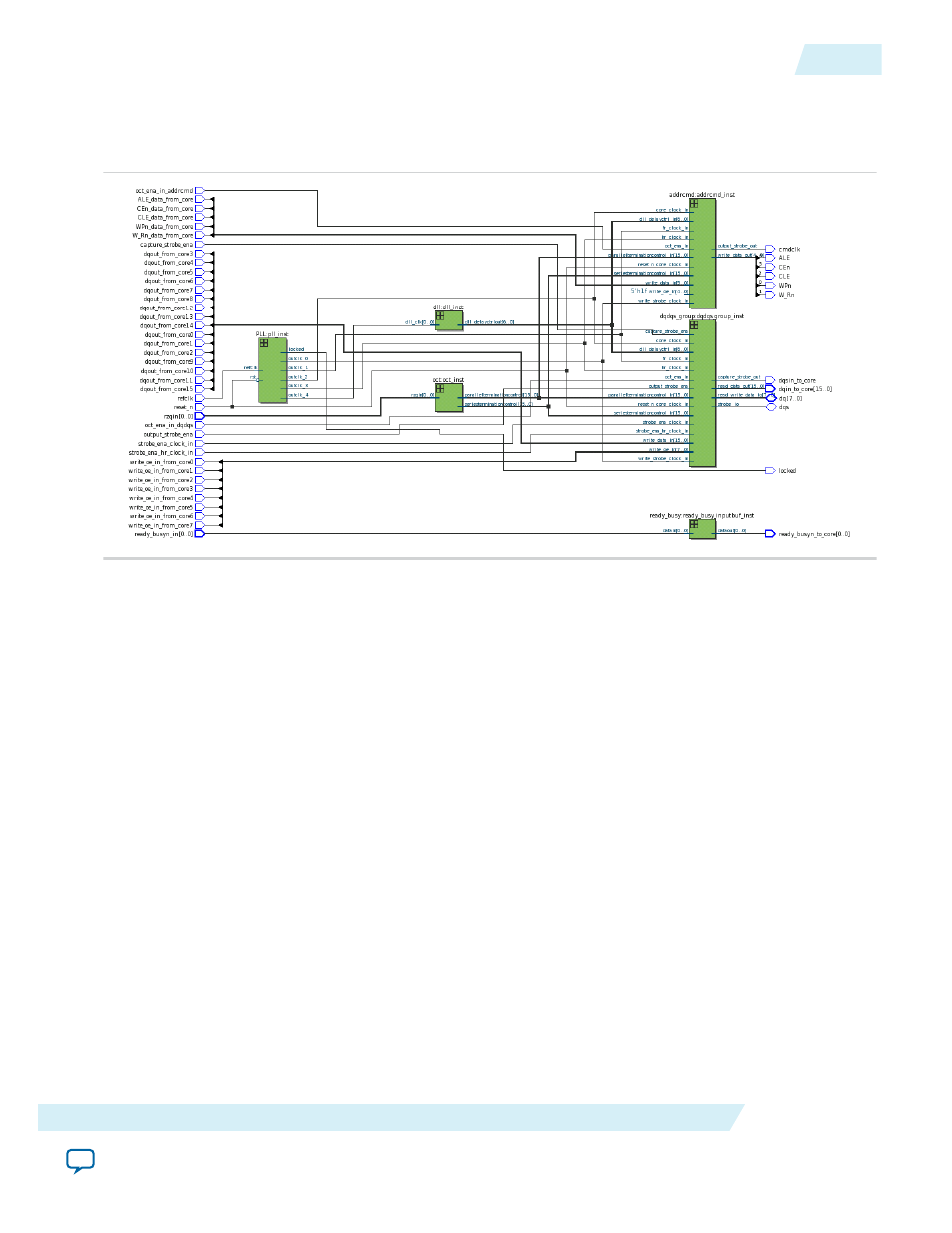

The following figure shows the RTL viewer for a NAND Flash simple design based on the ALTDQ_DQS2

IP core from this implementation.

Figure 29: RTL viewer for a NAND Flash simple design based on ALTDQ_DQS2

Implementation using the Altera PHYLite for Parallel Interfaces IP Core

You can configure the IP in a single Altera PHYLite for Parallel Interfaces IP core for multiple groups

(maximum 48 I/O pins each), instead of instantiating multiple ALTDQ_DQS2 configurations for various

settings/group.

The following lists the possible implementations when you target Arria 10 devices:

• Instantiates one Altera PHYLite for Parallel Interfaces IP core with three groups

• Bidirectional type for DQ and DQS

• Output type for Addr/Cmd

• Input type for the Ready signal

Note: Each group in the Altera PHYLite for Parallel Interfaces IP core can have 48 I/Os, and the IP

supports up to 18 groups.

ug_altera_phylite

2015.01.16

Implementation using the Altera PHYLite for Parallel Interfaces IP Core

55

Altera PHYLite for Parallel Interfaces IP Core User Guide

Altera Corporation