Altera CPRI v6.0 MegaCore Function User Manual

Page 44

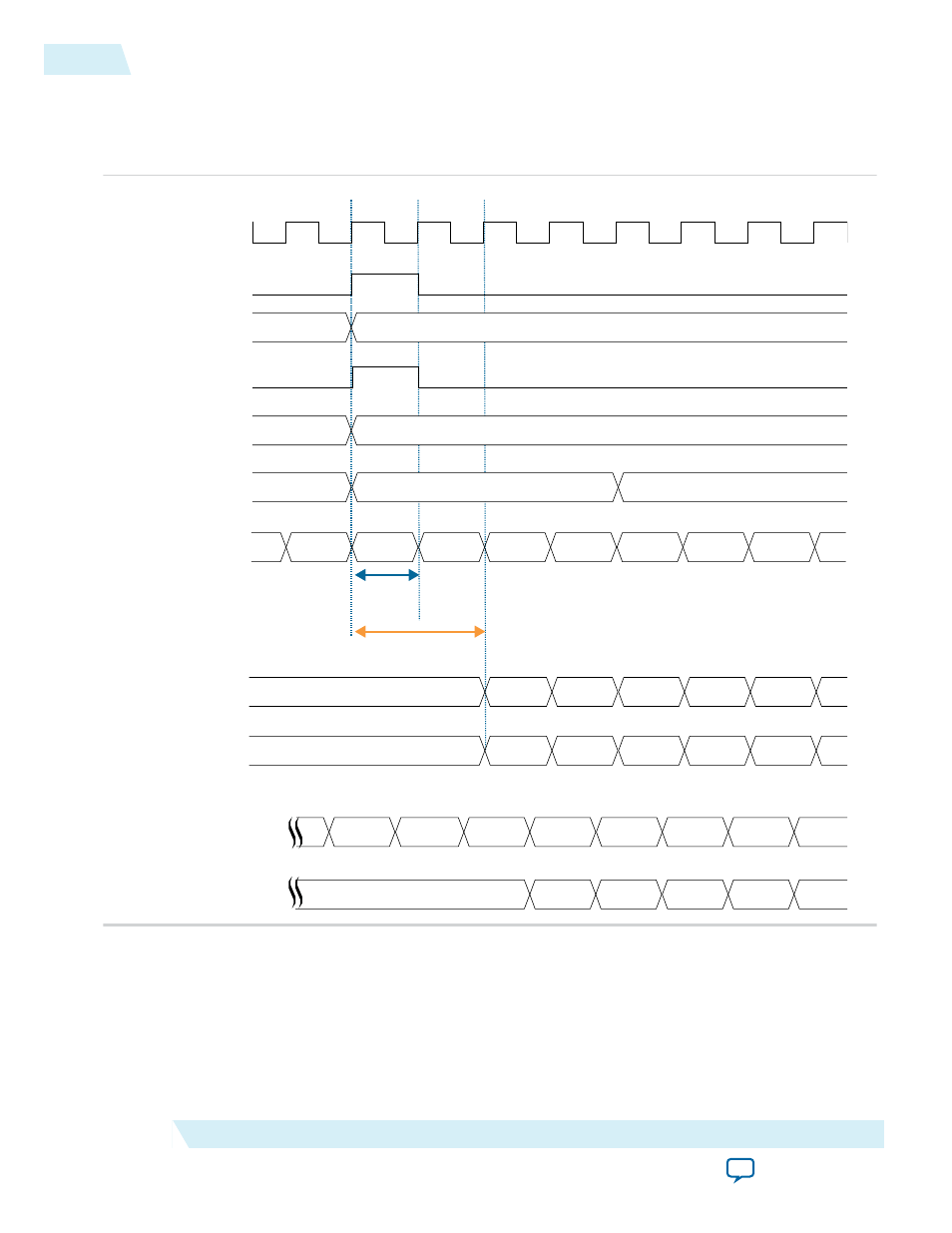

Figure 3-7: AUX TX Interface Timing Diagram with One Auxiliary Latency Cycle

Expected behavior on the AUX TX interface of a CPRI v6.0 IP core running at 0.6144 Gbps. Illustrates the

effect of setting the Auxiliary latency cycle(s) parameter to a a non-zero value. Shown for a CPRI v6.0 IP

core with Auxiliary latency cycle(s) set to the value of 1.

clock cycles write latency

4095

0

0

3

255

1

149

0

2

0

1

2

3

0

1

2

X

Data #1

Data #2

Data #3

Data #4

Data #5

Data #5

X

Mask #1

Mask #2

Mask #3

Mask #4

Mask #5

0

1

2

3

0

0

1

2

3

X

Data #1

Data #2

Data #3

Data #4

cpri_clkout

aux_tx_rfp

aux_tx_bfn

aux_tx_hfp

aux_tx_hfn

aux_tx_x

aux_tx_seq

aux_tx_data

aux_tx_mask

Sequence Nnumber

at actual CPRI frame

Actual frame data

Default one cpri_clkout cycle

delay to write

Default delay + 1

Auxiliary latency cycle(s) == 1:

3-14

AUX Interface Signals

UG-01156

2014.08.18

Altera Corporation

Functional Description