Avalon source-st signals, Avalon source-st signals -16 – Altera Viterbi Compiler User Manual

Page 34

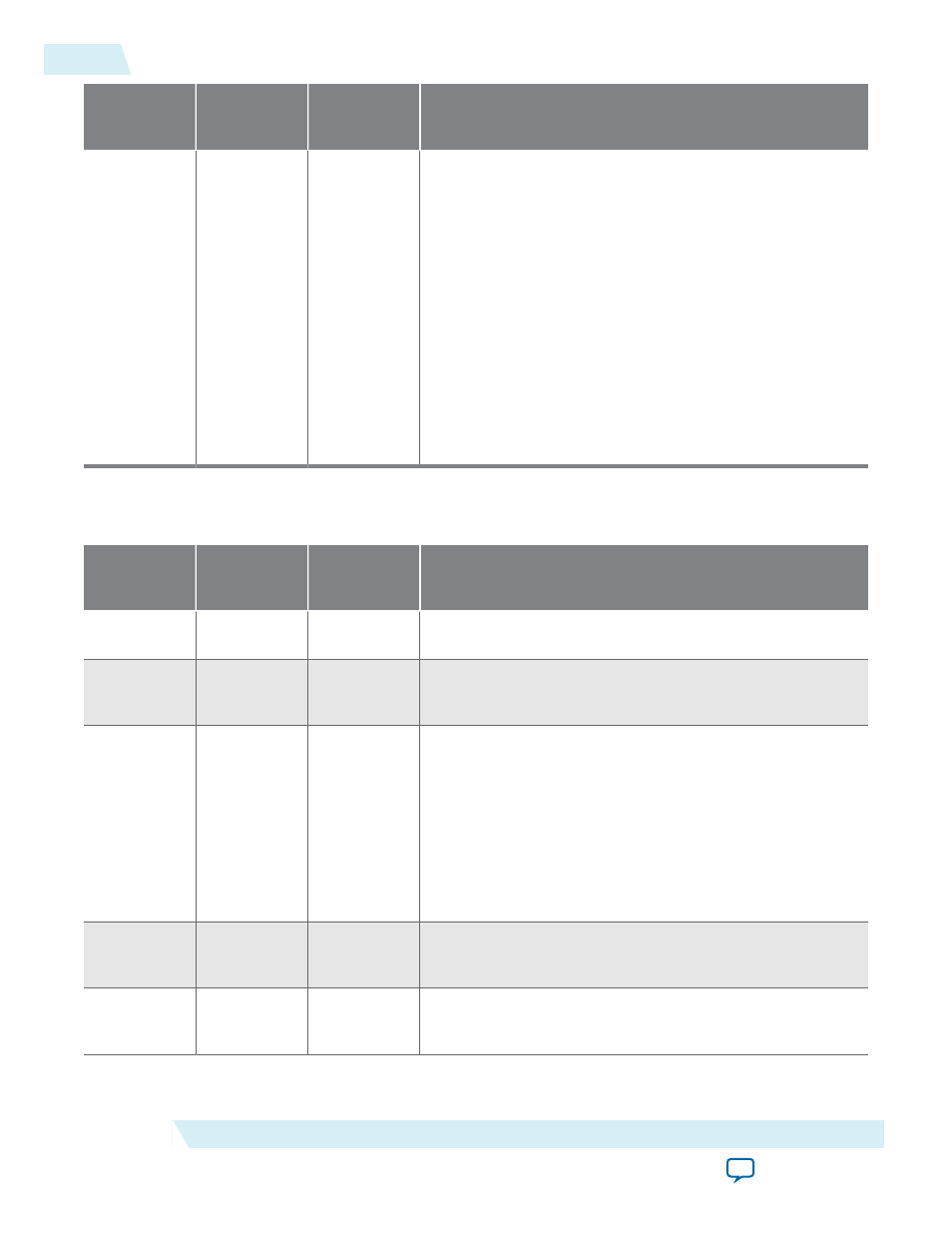

Signal Name

Avalon-ST

Name

Direction

Description

sink_data data

Input

In Qsys systems, this Avalon-ST-compliant data bus

includes all the Avalon-ST input data and configuration

signals. The signals are in the following order from MSB to

LSB:

•

In

•

State_node_sync

•

Ber_clear

•

Sel_code

•

Tb_type

•

Tb_length

•

Tr_init_state

•

Bm_init_state

•

Bm_init_value

•

Eras_symR

r

Avalon Source-ST Signals

Signal

Avalon-ST

Name

Direction

Description

decbit

dat

Output

The decbit signal contains output bits when source_val is

asserted.

source_eop eop

Output

End of packet (block) signal. if you select continuous

optimization, this signal is left open and you must remove it

from the testbench.

source_rdy ready

Input

Data transfer enable signal. The sink interface drives

source_rdy

and uses it to control the flow of data across the

interface.

ena

behaves as a read enable from sink to source.

When the source observes

source_rdy

asserted on the

clk

rising edge it drives, on the following

clk

rising edge, the

Avalon-ST data interface signals and asserts

source_val

.

The sink captures the data interface signals on the following

clk

rising edge. If the source is unable to provide new data,

it deasserts

source_val

for one or more clock cycles until it

is prepared to drive valid data interface signals.

source_sop sop

Output

Start of packet (block) signal. if you select continuous

optimization, this signal is left open and you must remove it

from the testbench.

source_val val

Output

Data valid signal. The IP core assers

source_val

high for

one clock cycle, whenever there is a valid output on the

decbit

signal.

3-16

Avalon Source-ST Signals

UG-VITERBI

2014.12.15

Altera Corporation

Viterbi IP Core Functional Description