Altera Viterbi Compiler User Manual

Page 8

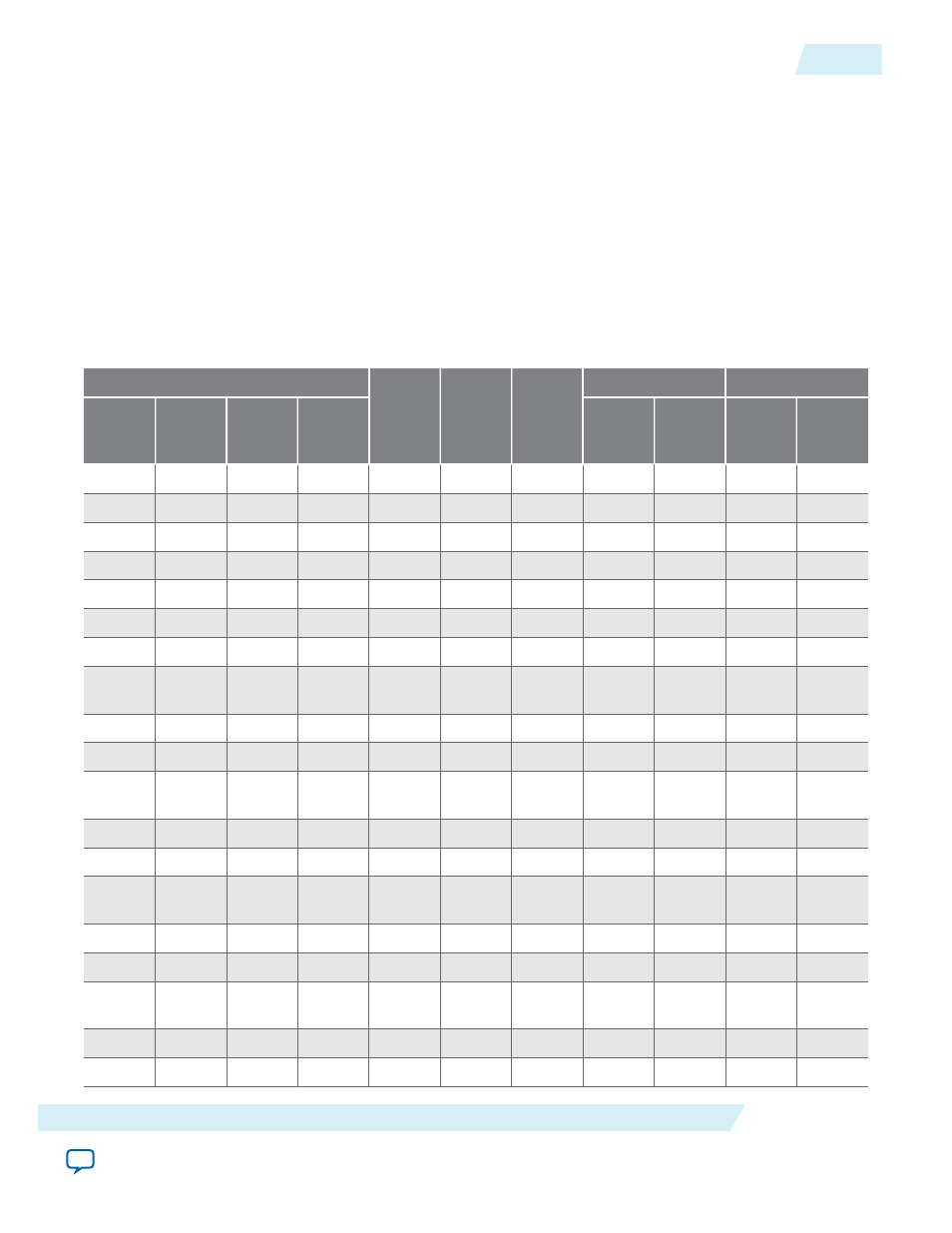

Parallel Architecture

The typical expected performance for a parallel Viterbi IP core uses the Quartus II software with the Arria

V (5AGXFB3H4F40C4), Cyclone V (5CGXFC7D6F31C6), and Stratix V (5SGSMD4H2F35C2) devices.

The following parameters apply:

• v = 6 ×L

• N = 2

where:

• v is the traceback length

• L is the constraint length

• N is the number of coded bits

Table 1-4: Typical Performance

Parameters

Device

ALMs

fMAX

(MHz)

Memory

Registers

softbits

L

Optimiz

ation

Best

State

Finder

M10K

M20K

Primary Seconda

ry

5

3

—

On

Arria 10 420

400

--

5

500

63

7

3

—

On

Arria 10 453

351

--

5

534

75

3

3

—

Off

Arria 10 396

423

--

5

473

39

5

3

—

Off

Arria 10 420

400

--

5

500

63

7

3

—

Off

Arria 10 453

351

--

5

534

75

3

7

Block

Off

Arria 10 1,454

354

--

3

817

154

3

7

Block

Off

Arria V 1,537

201

5

--

1,166

168

3

7

Block

Off

Cyclone

V

1,544

149

5

--

1,167

88

3

7

Block

Off

Stratix V 1,521

352

--

3

1,167

154

3

3

—

Off

Arria V 378

237

5

--

456

67

3

3

—

Off

Cyclone

V

378

200

5

--

456

84

3

3

—

Off

Stratix V 378

405

--

5

455

45

5

3

—

Off

Arria V 397

210

5

--

483

68

5

3

—

Off

Cyclone

V

397

188

5

--

484

81

5

3

—

Off

Stratix V 396

406

--

5

482

92

3

3

—

On

Arria V 378

237

5

--

456

67

3

3

—

On

Cyclone

V

378

200

5

--

456

84

3

3

—

On

Stratix V 378

405

--

5

455

45

5

3

—

On

Arria V 397

210

5

--

483

68

UG-VITERBI

2014.12.15

Viterbi IP Core Performance and Resource Utilization

1-5

About the Viterbi IP Core

Altera Corporation