Ethernet phy – Altera LCD Multimedia HSMC User Manual

Page 27

2–19

Altera Corporation

LCD Multimedia HSMC

August 2008

Interfaces/ Connectors

Ethernet PHY

Ethernet support is provided via the National Semiconductor DP83848C

Ethernet Physical Layer Transceiver chip and an RJ-45 connector (J5).

lists Ethernet PHY board reference and manufacturing

information.

The DP83848C device has the following features:

■

Single Port 10/100 Mb/s Ethernet Physical Layer Transceiver

■

Supports both 100Base-T and 10Base-T Ethernet protocols

■

Supports Auto-MDIX for 10/100 Mb/s

The DP83848C is one port Fast Ethernet PHY Transceivers supporting

IEEE 802.3 physical layer applications at 10 Mbps and 100 Mbps. The

DP83848C provides Media Independent Interface (MII) to connect

DP83848C to a MAC in the FPGA.

shows the pinout of Ethernet PHY with HSMC connector.

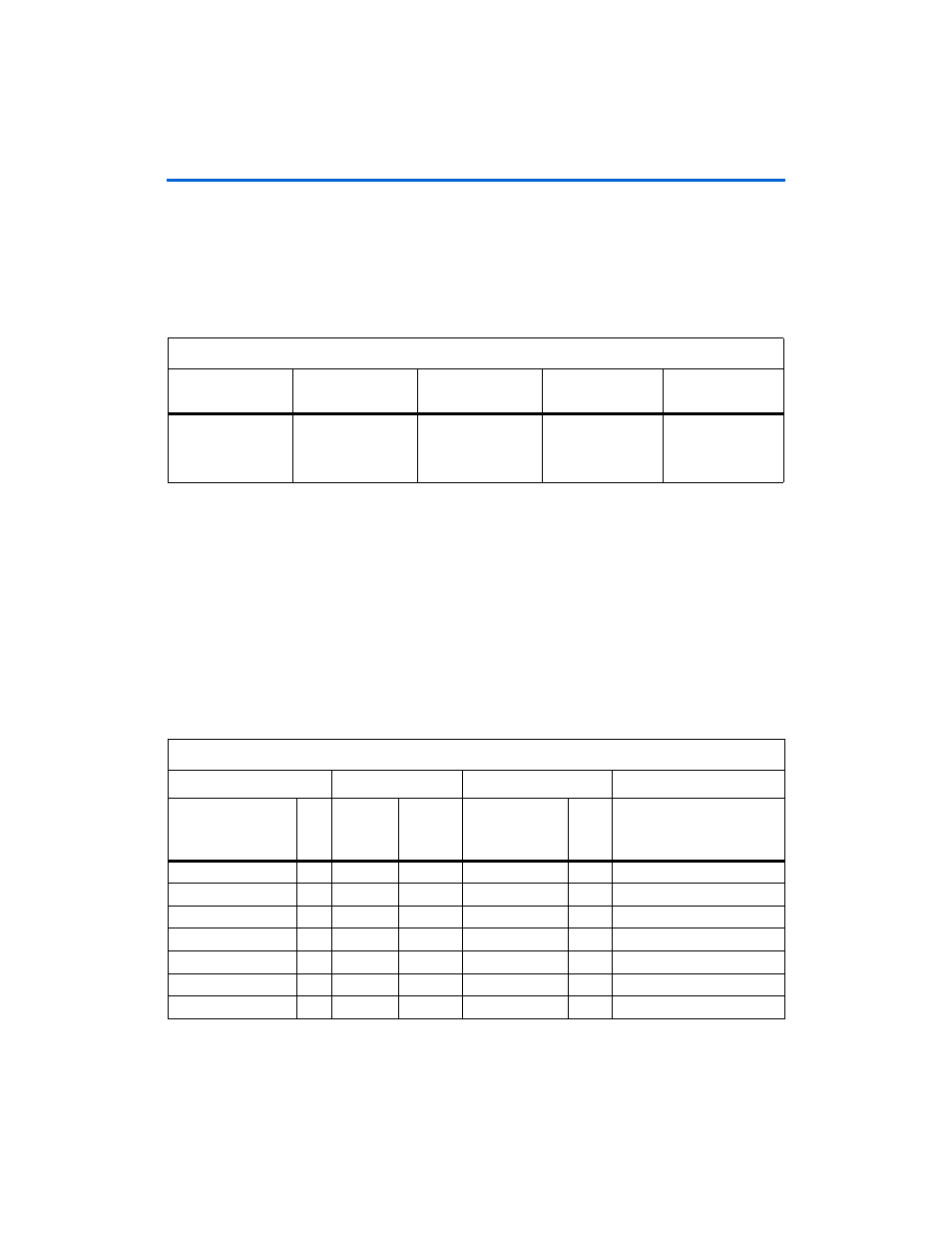

Table 2–12. Ethernet PHY Manufacturing Information

Board Reference

Device Description

Manufacturer

Manufacturer Part

Number

Manufacturer

Website

U2

Single Port 10/100

Mb/s Ethernet

Physical Layer

Transceiver

National

Semiconductor

DP83848C

Table 2–13. Ethernet PHY Pinout with HSMC Connector

HSMC Connector

MAX II

Ethernet PHY

Signal Name

Pin

No.

HSMC

Connector

Side Pin

Device

Side Pin

Signal Name

Pin

No.

Description

HC_TX_CLK

158

A13

T2

TX_CLK

1

MII Transmit Clock

HC_TX_EN

125

F18

R3

TX_EN

2

MII Transmit Enable

HC_TXD[0]

127

F17

P4

TXD0

3

MII Transmit Data bit 0

HC_TXD[1]

131

E17

R1

TXD1

4

MII Transmit Data bit 1

HC_TXD[2]

133

E18

R2

TXD2

5

MII Transmit Data bit 2

HC_TXD[3]

137

E16

P2

TXD3

6

MII Transmit Data bit 3

HC_ETH_RESET_N

121

F16

T3

Eth_RESET_N

29

DP83848C Reset