Altera LCD Multimedia HSMC User Manual

Page 46

Altera Corporation

A–2

August 2008

LCD Multimedia HSMC

1

The Cyclone III FPGA Starter Board schematic can be found

at:<installation directory>/board_design_files/schematic/

cycloneIII_3c25_start.

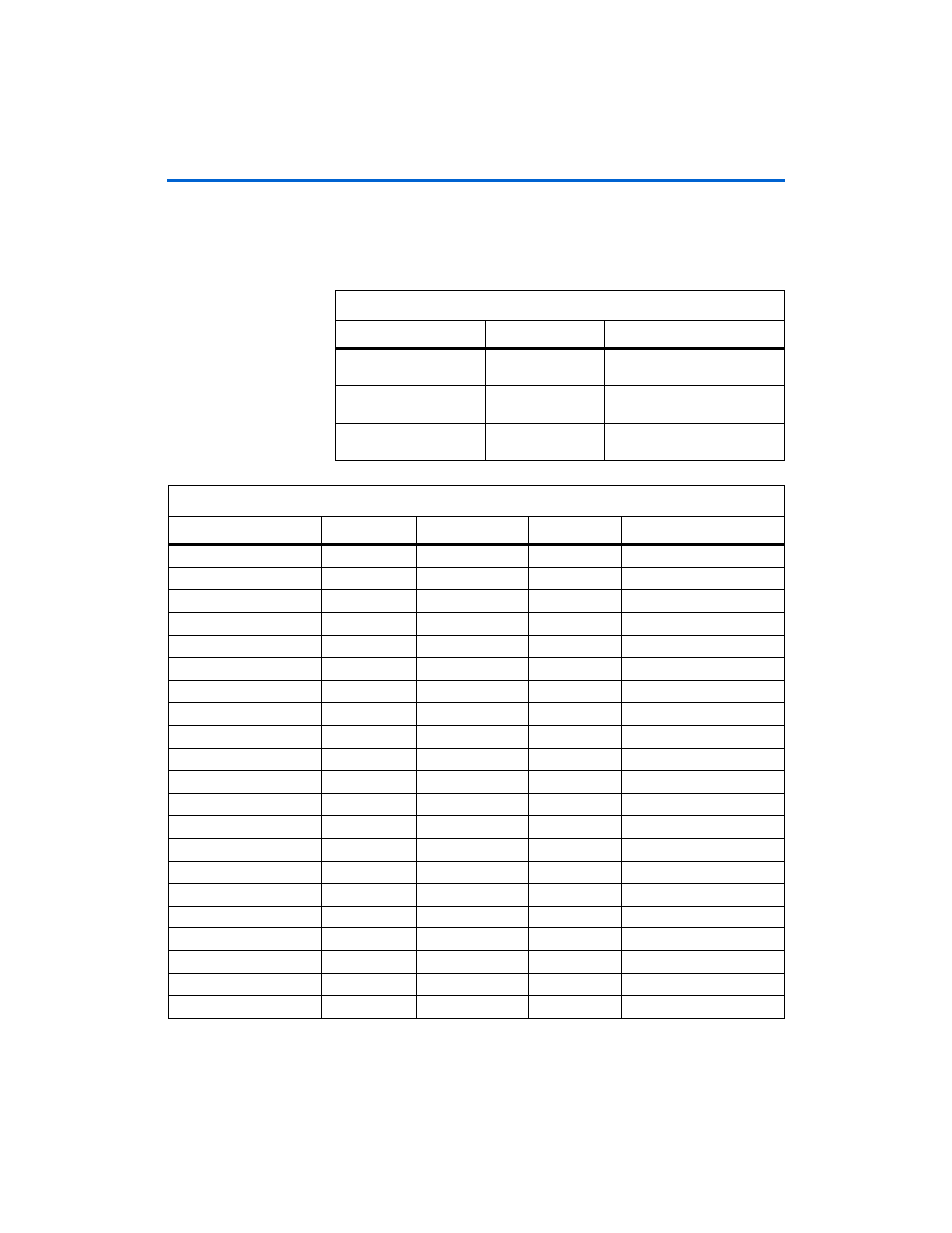

Table A–1. Settings to avoid unwanted noise across signals

When using this function

Disable this chip

Required Setting

Video Decoder

Ethernet PHY (U2)

Set HC_ETH_RESET_N to

logic 0

Touch Panel

Ethernet PHY (U2)

Set HC_ETH_RESET_N to

logic 0

Ethernet PHY

Video Decoder (U8) Set HC_TD_RESET to logic 0

Avoid using touch-panel.

Table A–2. HSMC

.FPGA Pinout

Signal Name

HSMC Pin

FPGA Pin

Direction

Type

HSMC_SDA

33

E1

Bidirectional

2.5 V

HSMC_SCL

34

F3

Bidirectional

2.5 V

HSMC_TCK

35

J1

HSMC_TMS

36

J2

HSMC_TDI

37

J6

HSMC_TDO

38

J5

HSMC_CLKOUT0

39

A1

Output

2.5

V

HSMC_CLKIN0

40

A9 Input

2.5

V

HSMC_CLKOUT_p1

95

D14

Output

2.5

V

HSMC_CLKIN_p1

96

F17

Input 2.5

V

HSMC_CLKOUT_n1

97

C14

Output 2.5

V

HSMC_CLKIN_n1

98

F18

Input

2.5 V

HSMC_CLKOUT_p2

155

U18

Output

2.5 V

HSMC_CLKIN_p2

156

N17

Input

2.5 V

HSMC_CLKOUT_n2

157

V18

Output 2.5

V

HSMC_CLKIN_n2

158

N18

Input

2.5 V

HSMC_D0

41

H6

Bidirectional

2.5 V

HSMC_D1

42

D3

Bidirectional

2.5 V

HSMC_D2

43

M5 Bidirectional

2.5

V

HSMC_D3

44

L6

Bidirectional

2.5 V

HSMC_D4

47

T1

Bidirectional

2.5 V