Altera Stratix III Development Board User Manual

Page 45

Chapter 2: Board Components

2–37

General User Interfaces

May 2013

Altera Corporation

Stratix III 3SL150 Development Board

Reference Manual

f

For more information, contact Optrex Am

or New Japan

Radio at

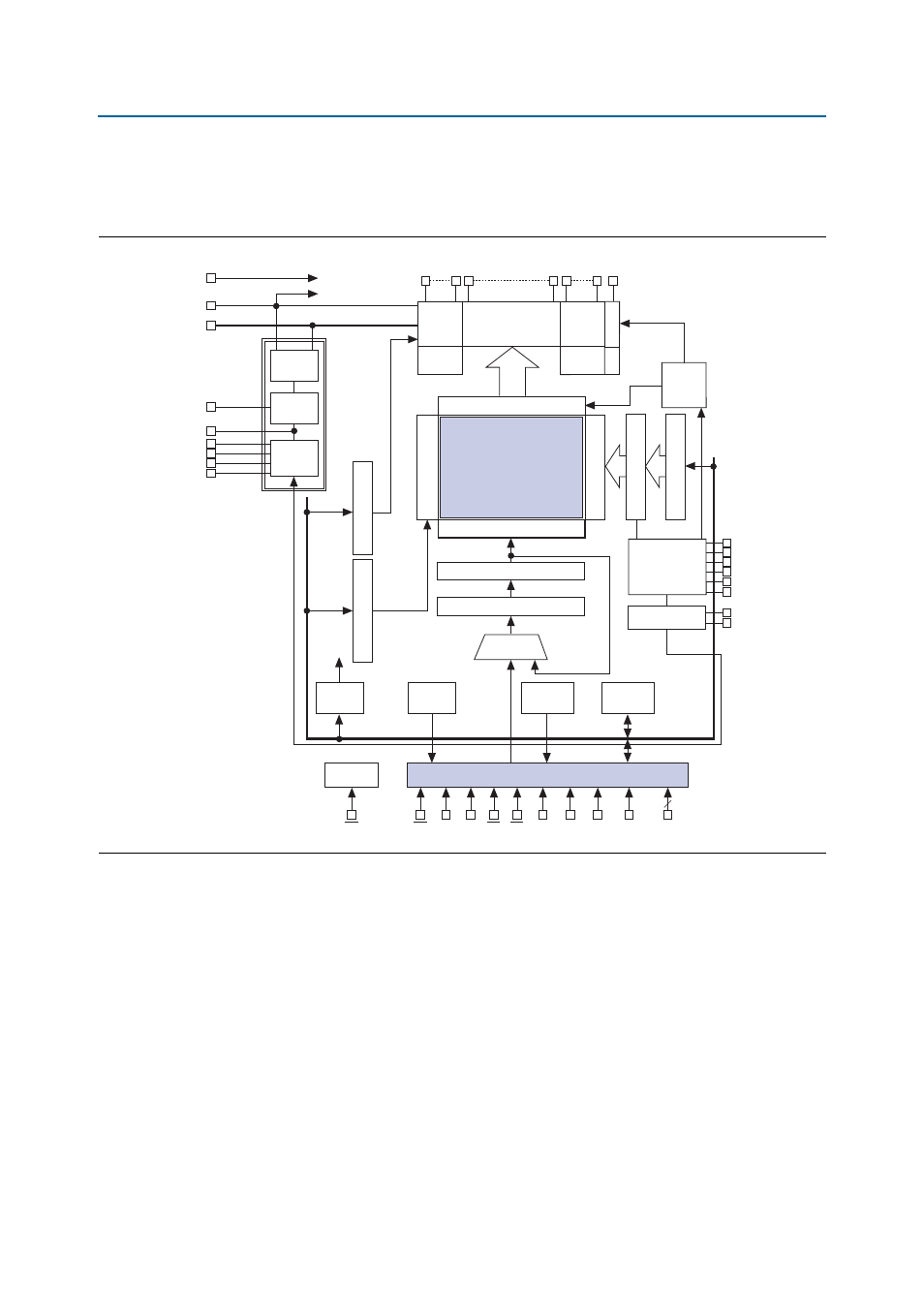

Figure 2–12. Graphics LCD Functional Block Diagram of Display Driver

Segment Drivers

Common

Drivers

Shift

Register

Shift

Register

Common

Drivers

Display Data RAM

65 X 132 = 8,580-bit

Display Data Latch

Low Address Deocder

Line Address Deocder

Column Address Decoder

Vss

VDD

Oscillator

Bus Holder

Busy Flag

Instruction

Decoder

Status

Voltage

Followers

Voltage

Regulator

Voltage

Converter

Multiplexer

Line Counter

Initial Displa

y Line

Common Direction

P

age Address Register

Column Address Counter

Column Address Register

MPU Interface

Reset

Common

Timing

Display Timing

VR

C1+/C1-

C2+/C2-

C3-

Vss2

Vout

V1 to V6

Internal

Power

Circuits

C0 - - - C21

C63 - - - C32

MS

S0 - - - S131

FR

FRS

CL

CLS

DOF

OSC1

OSC2

D5 to D0

P/S

D6

(SCL)

D7

(SI)

C86

A0

CS2

CS1

WR

Status

Internal Bus Line

RD

RES

COMM