Zilog EZ80L92 User Manual

Page 78

UM012913-0407

Schematic

Diagrams

eZ80L92 Development Kit

User Manual

74

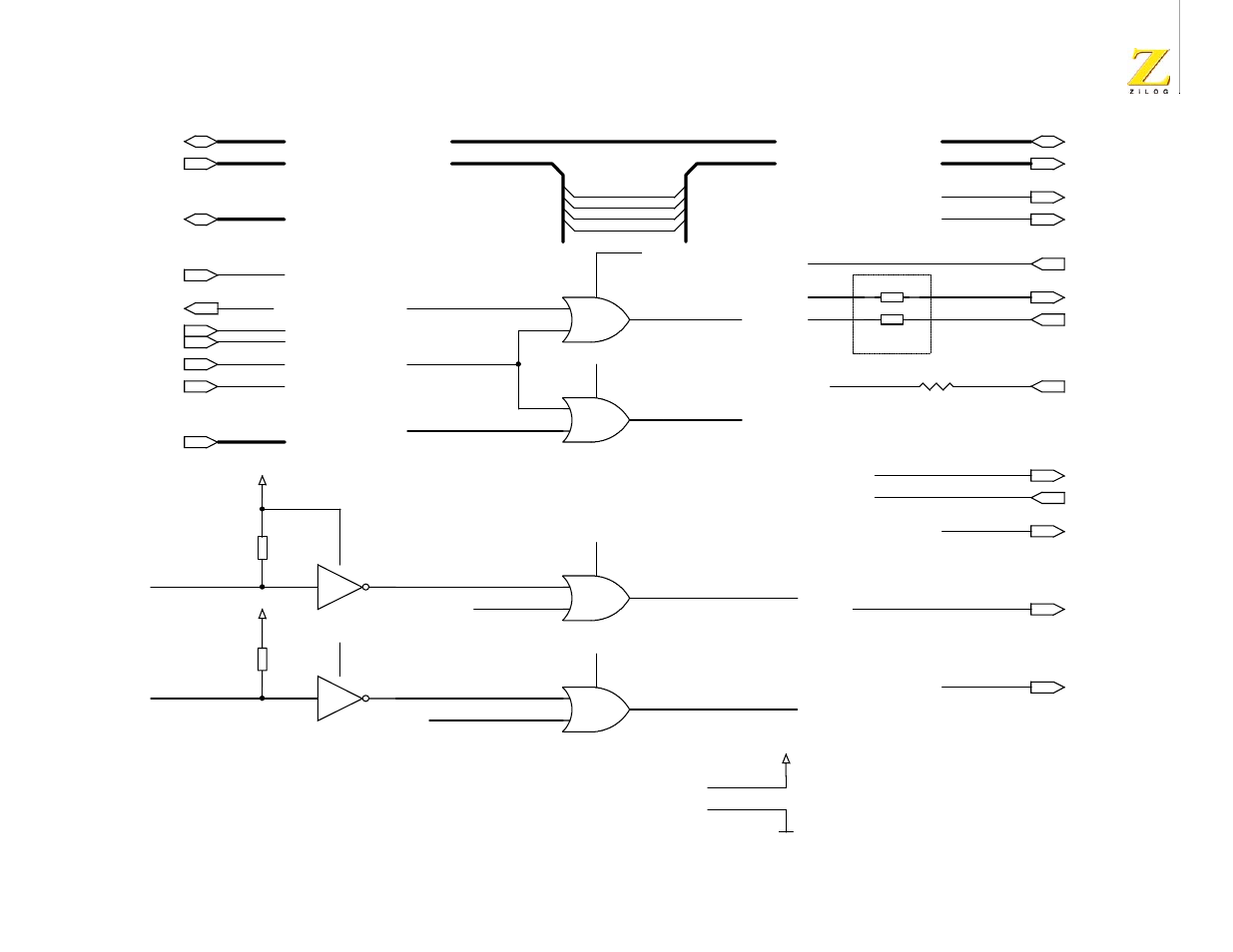

Figure 30. eZ80L92 Module Schematic Diagram, #9 of 9—Control Logic

=

=

=

=

=

=

=

=

=

=

don’t stuff

=

PD3 and PD5

not used here

-CS1 and-CS2

not used

here

only A0,A1,A2,A3

are used here

-RD

-WR

-ETHRD

-ETHWR

VSS

VDD

SD[0..7]

D[0..7]

SA[0..3]

A[0..23]

-SLEEP

-ACTIVE

D[0..7]

SD[0..7]

A[0..23]

SA[0..3]

SA0

A0

SA1

A1

SA2

A2

SA3

A3

PD[0..7]

-CS[0..3]

-CSFLASH

-RESFLASH

-RESET

IRDA_TXD

PD0

IRDA_RXD

PD1

IRDA_SD

-RESET

-RD

-WR

-ETHRD

-ETHWR

-CS3

-CSETH

-CS0

-CSFLASH

IRDA_SD

PD7

PD6

ETHIRQ

PD4

-DIS_IRDA

-DIS_FL

IR_SD

PD2

DIS_IRDA

-DIS_FL

-DIS_IRDA

-WAIT

-WAIT

VDD

VDD

DIS_FL

V3.3

GND

R17

10k

0603

R35

0

R30

10k

0603

R14

0R

U6D

74LCX32

TSSOP14

12

13

11

14

U2C

74LVC04/SO

5

6

14

U6A

74LCX32

TSSOP14

1

2

3

14

U2B

74LVC04/SO

3

4

14

R15

0R

U6B

74LCX32

TSSOP14

4

5

6

14

U6C

74LCX32

TSSOP14

9

10

8

14

-RD

-WR

-ETHRD

-ETHWR

SD[0..7]

D[0..7]

A[0..23]

SA[0..3]

ETHIRQ

-SLEEP

-ACTIVE

PD[0..7]

-CS[0..3]

-DIS_FL

-DIS_IRDA

-CSFLASH

-RESFLASH

IRDA_TXD

IRDA_SD

IRDA_RXD

-RESET

IOCHRDY

-WAIT