Table 4-3, Tnc gpio definition, Table 4-4 – Artesyn NITX-315/NITX-315-ET Installation and Use (August 2014) User Manual

Page 67: Topcliff gpio configuration, Functional description

Functional Description

NITX-315/NITX-315-ET Installation and Use (6806800L71D)

67

The PCA9557PW provides eight user defined GPIOs, 4 GPI and 4 GPO with 5V referenced on

one internal header P4. See

.

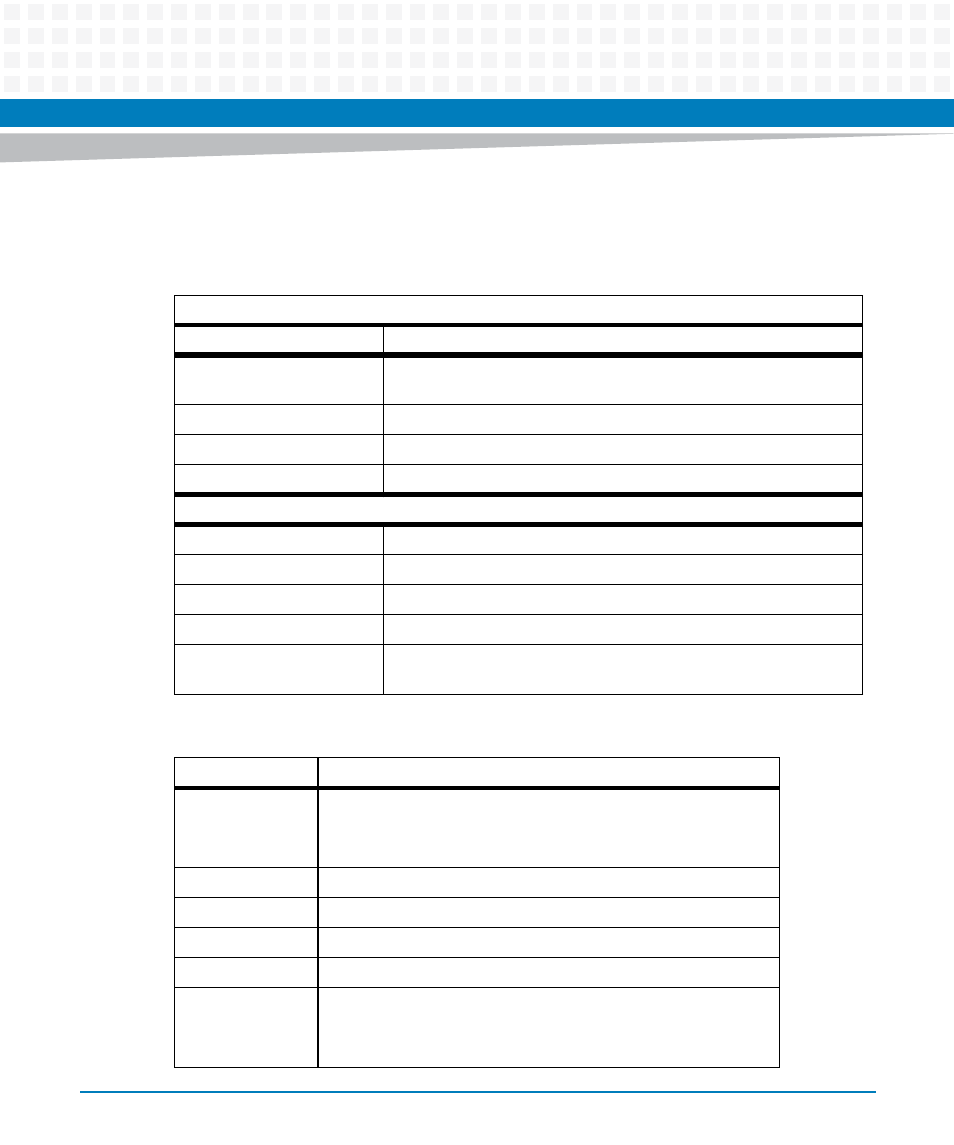

Table 4-3 TNC GPIO Definition

5 Core-well GPIOs (turned off during sleep mode)

Name

Function

GPIO[4]

LPC[0] clock buffer strength control, Also muxed with

WDT_TIMEOUT

GPIO[3:2]

Defines CMC base address

GPIO[1]

Reserved

GPIO[0]

Defines boot flash from SPI or LPC

9 Sus well GPIOs accessible during S3 sleep state (GPIO SUS[0:8])

GPIO_SUS[8]

Defines number of ranks enabled

GPIO_SUS[6:5]

Defines memory device densities

GPIO_SUS[2]

Muxed with LVDS BKLTCTL

GPIO_SUS[1]

Muxed with LVDS BKLTEN

GPIO_SUS[0]

Defines memory device width (x16 or x8) Also muxed with LVDS

VDDEN

Table 4-4 Topcliff GPIO Configuration

Name

Function

GPIO0

USB MUX control.

Low: USB port5 is routing to Mini PCI-E slot

High : USB port5 is routing to eUSB slot

GPIO1

NC

GPIO2

NC

GPIO3

NC

GPIO4

NC

GPIO5

Client USB power detect.

Low: No Client USB power existence

High: Client USB power existence