Register communication – BECKHOFF KL3311 User Manual

Page 17

Register Description

KL3311, KL3312, KL3314 and KL3302

15

the terminal contacts), a gain register (R21) is implemented, which is

identical for both sets of registers.

Compensation can be carried out as follows:

First, the offset is carried out with 0V input voltage, reference temperature

deactivated and linearization switched off. 0xF100 is entered in the feature

register. This is followed by gain compensation with a maximum voltage of

125 mV (typical value: 70 mV). For this terminal setting with deactivated

manufacturer scaling, the voltage is displayed with 4

μV per digit.

Gain and offset compensation of the thermocouple voltage is carried out

separately for each channel.

In the next step, the temperature of the reference point is compensated. To

this end, a thermocouple has to be selected via the feature register, and

reference point temperature compensation must be active (R32 0x1006

type K). With short-circuited inputs (0 V), the temperature of the terminal

contacts is determined, and the temperature output by the terminal

(measured via an internal temperature sensor) is set accordingly (via R21).

The reference point temperature only has to be calibrated once for each

terminal, i.e. R21 is identical for both channels.

Register communication

Register access via

process data exchange

Bit 7=1

bin

: Register mode

If bit 7 of the control byte is set, then the first two bytes of the user data are

not used for exchanging process data, but are written into or read from the

terminal's register set.

Bit 6=0

bin

: read

Bit 6=1

bin

: write

Bit 6 of the control byte specifies whether a register should be read or

written. If bit 6 is not set, then a register is read out without modifying it.

The value can then be taken from the input process image.

If bit 6 is set, then the user data is written into a register. As soon as the

status byte has supplied an acknowledgement in the input process image,

the procedure is completed (see example).

Bit 0 to 5: Address

The address of the register that is to be addressed is entered into bits 0 to

5 of the control byte.

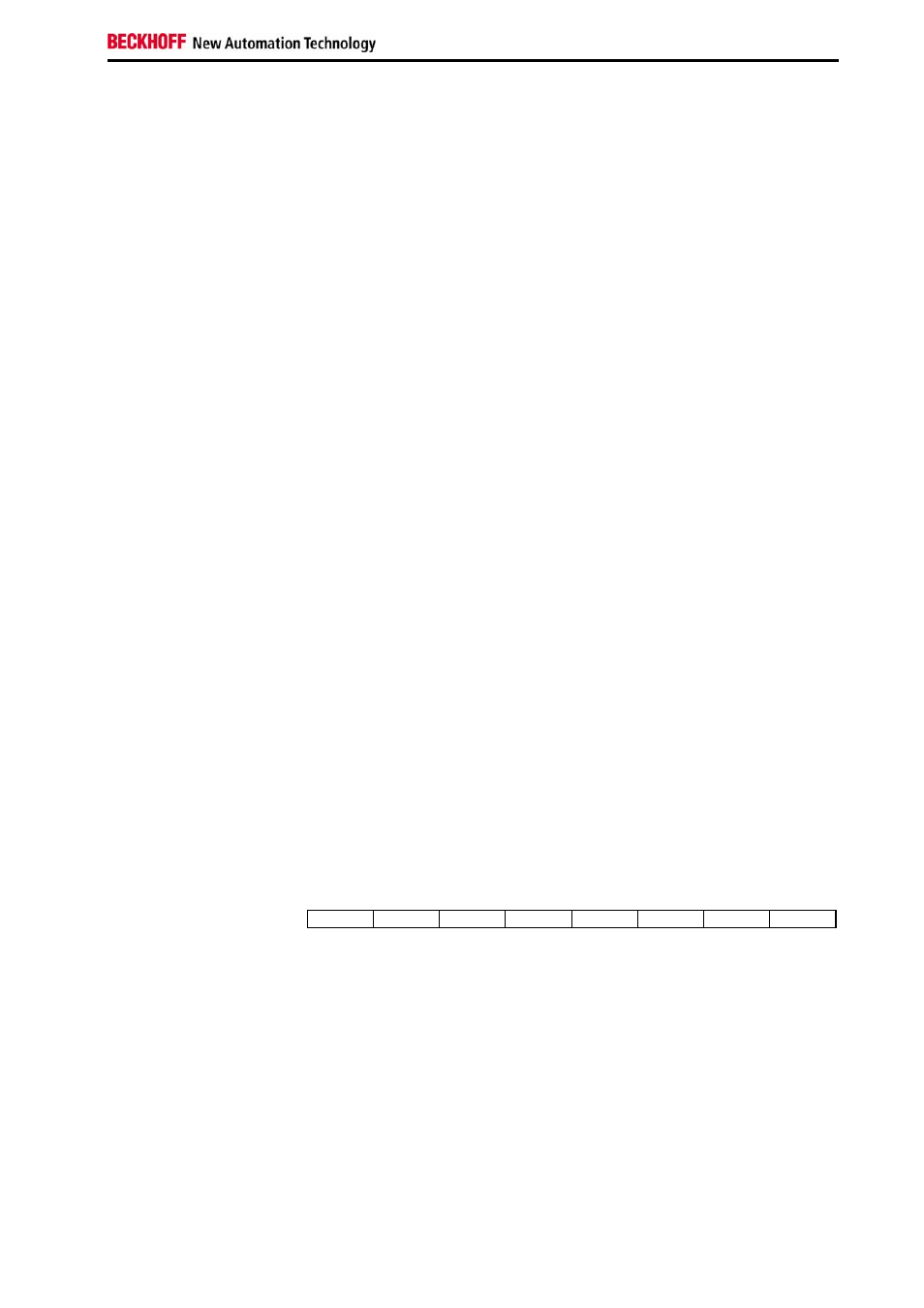

Control byte in

register mode

MSB

REG=1

W/R

A5

A4

A3

A2

A1

A0

REG = 0

bin

: Process data exchange

REG = 1

bin

: Access to register structure

W/R = 0

bin

: Read register

W/R = 1

bin

: Write register

A5...A0 = register address

Address bits A5 to A0 can be used to address a total of 64 registers.