BECKHOFF ET1100 User Manual

Page 86

PDI description

III-72

Slave Controller

– ET1100 Hardware Description

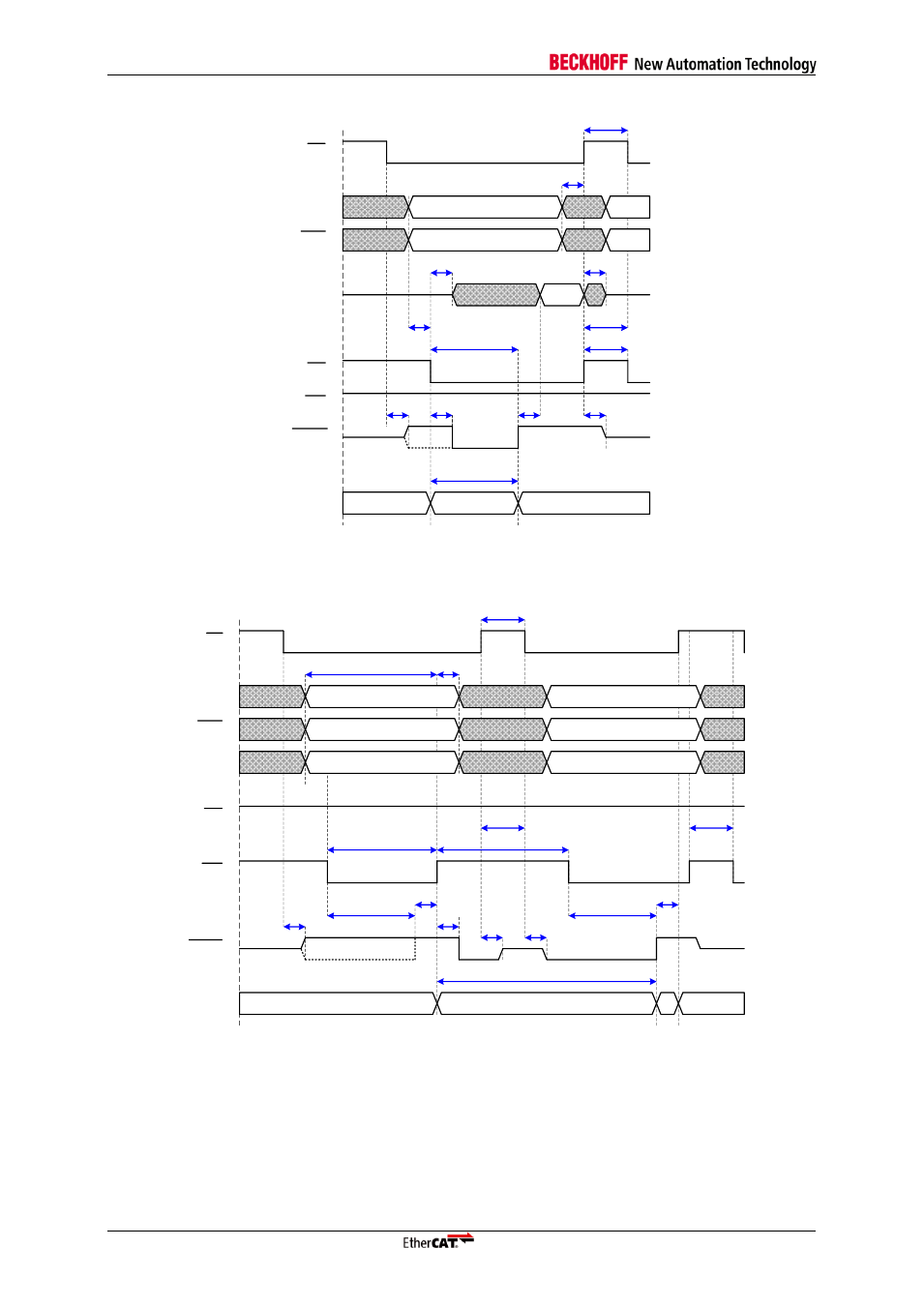

t

CS_RD_to_DATA_release

BHE

t

ADR_BHE_setup

CS

BHE

RD

WR

DATA

BUSY

DATA

ADR

ADR

t

CS_to_BUSY

t

read

t

RD_to_BUSY

t

RD_delay

t

CS_delay

t

BUSY_to_DATA_valid

t

ADR_BHE_to_DATA_invalid

t

RD_to_DATA_driven

t

CS_to_BUSY_release

BHE

ADR

t

RD_CS_overlap

(with preceding write access)

Internal

state

Reading ADR

Idle

t

read_int

Idle

Figure 25: Read access (without preceding write access)

BHE1

CS

BHE

WR

RD

DATA

BUSY

ADR1

ADR

t

WR_active

t

CS_delay

t

WR_delay

t

ADR_BHE_DATA_hold

DATA1

t

ADR_BHE_DATA_setup

t

CS_to_BUSY

(with preceding write access)

t

WR_to_BUSY

t

write

t

CS_to_BUSY

t

CS_to_BUSY

t

BUSY_to_WR_CS

Internal

state

Writing ADR1

Idle

Idle

t

CS_WR_overlap

t

write_int

Writing ADR2

t

write

BHE2

ADR2

DATA2

t

BUSY_to_WR_CS

t

CS_WR_overlap

Figure 26: Write access (write after rising edge nWR, without preceding write access)