BECKHOFF ET1100 User Manual

Page 97

Advertising

PDI description

Slave Controller

– ET1100 Hardware Description

III-83

Parameter

Min

Max

Comment

t

EEPROM_LOADED_to_IRQ

0 ns

IRQ valid after EEPROM_LOADED

EtherCAT device output

EtherCAT device input

CPU_CLK_IN*

t

IN_setup

t

IN_hold

t

CLK_to_OUT_valid

Input

t

CLK_to_OUT_invalid

Output

t

CLK

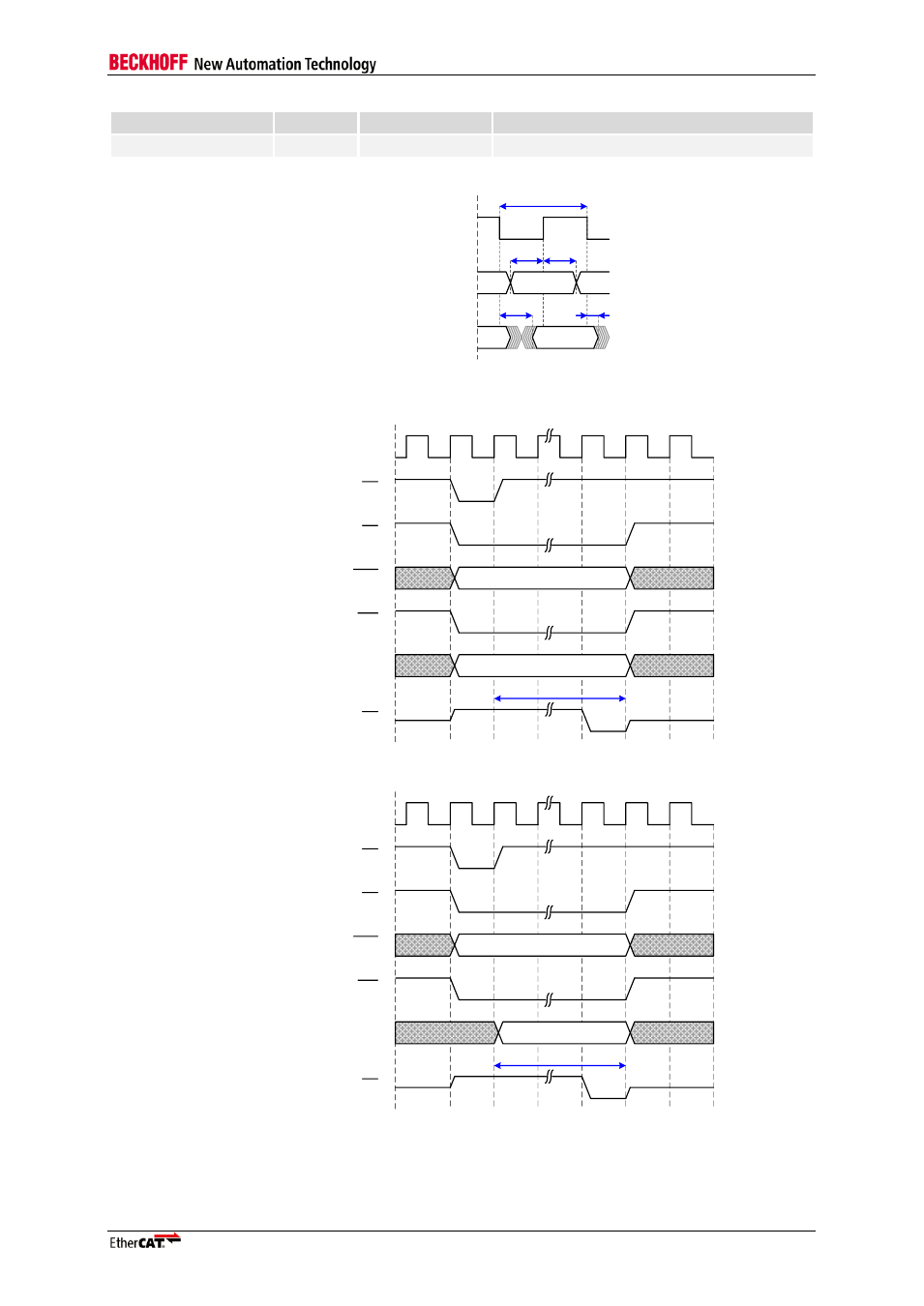

Figure 32: Basic synchronous µController interface timing (*refer to timing diagram for relevant

CPU_CLK_IN edges)

CPU_CLK_IN

TS

CS

ADR, BHE

DATA

TA

ADR, BHE

RD/WR

DATA

t

Write

Figure 33: Write access (CS together with TS, Write DATA together with CS, CS and TA on rising edge)

CPU_CLK_IN

TS

CS

ADR, BHE

DATA

TA

ADR, BHE

RD/WR

DATA

t

Write

Figure 34: Write access (CS together with TS, Write DATA after CS, CS and TA on rising edge)

Advertising