Your hal tester – Seaward ClareHAL User Manual

Page 161

160

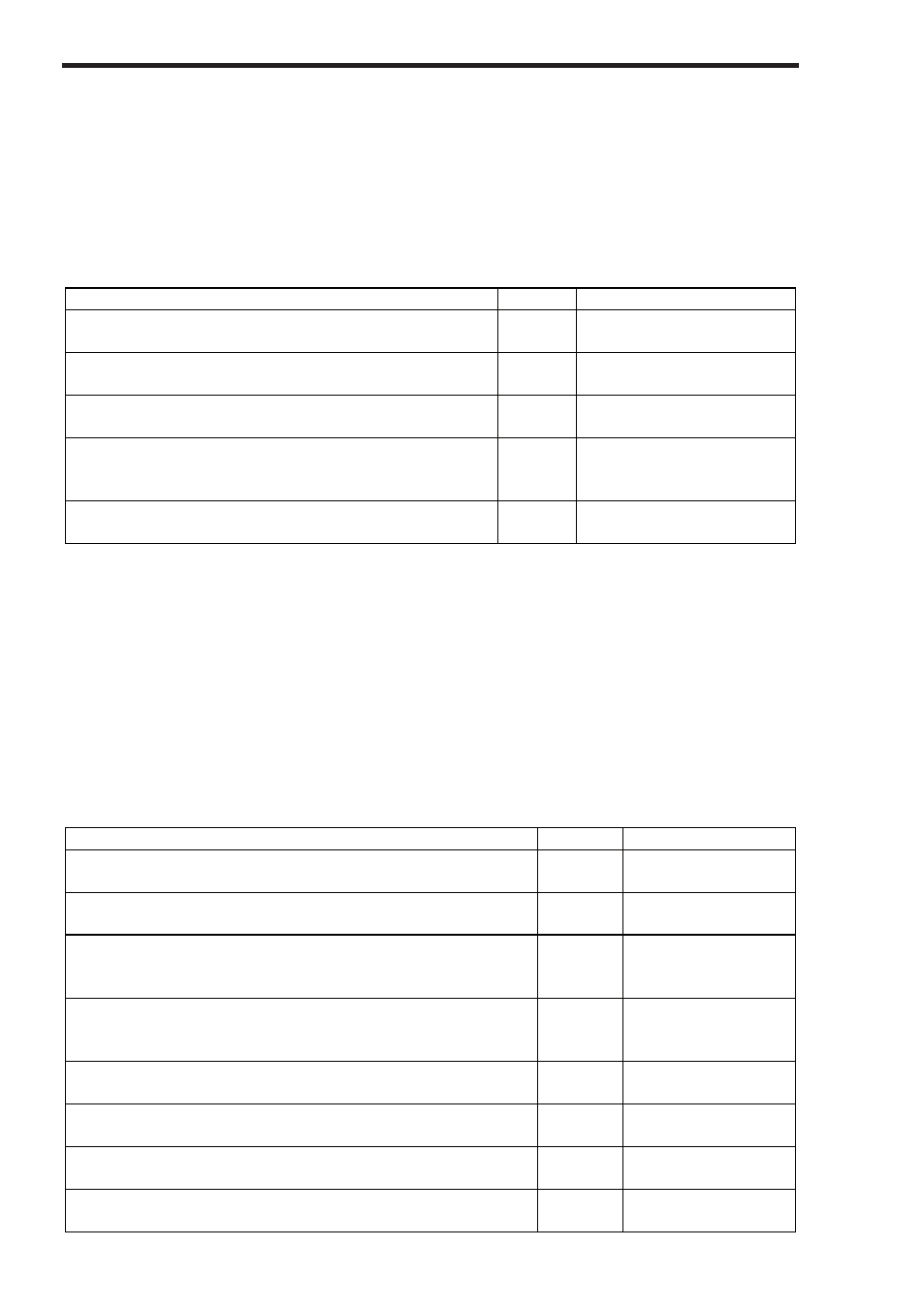

There are two distinct sets of test states: those that can be sent as part

of an interim ACK, and those that can be sent as part of a final ACK:

Test states only sent as part of an interim ACK

These states have the highest bit clear to differentiate them from final

result states:

SSSVAL_HAL_TSTATE_COMMAND_RECEIVED

0x00

First interim ACK.

SSSVAL_HAL_TSTATE_WAITING_FOR_START

0x01

Waiting for start conditions

(sent once per second).

SSSVAL_HAL_TSTATE_PREPARING_HARDWARE

0x02

Getting hardware and

channel relays ready

SSSVAL_HAL_TSTATE_RAMPING_TO_TARGET

0x03

Test has started, ramping

voltage up.

SSSVAL_HAL_TSTATE_HOLDING

0x04

Hold phase, final reading

captured at end of this

phase

SSSVAL_HAL_TSTATE_RAMPING_TO_ZERO

0x05

Ramping voltage back to

zero.

Test states only sent as part of a final ACK

These states have the highest bit set to differentiate them from on-

going test states:

SSSVAL_HAL_TSTATE_PASSED

0x80

Test passed

SSSVAL_HAL_TSTATE_FAILED_UPPER_LIMIT

0x90

Test failed: result is

above upper limit

SSSVAL_HAL_TSTATE_FAILED_LOWER_LIMIT

0x91

Test failed: result is

below lower limit

SSSVAL_HAL_TSTATE_ABORTED_HW_SHUTDOWN

0xA0

Test aborted: no

specific cause

detected

SSSVAL_HAL_TSTATE_ABORTED_GUARD_SWITCH

0xA1

Test aborted: guard

switch input was

open

SSSVAL_HAL_TSTATE_ABORTED_KEY

0xA2

Test aborted: abort

key was pressed

SSSVAL_HAL_TSTATE_ABORTED_OVER_CURRENT

0xA3

Test aborted: over-

current detected

SSSVAL_HAL_TSTATE_ABORTED_OVER_TEMP

0xA4

Test aborted: over-

temperature detected

SSSVAL_HAL_TSTATE_ABORTED_ARC

0xA5

Test aborted: arc

detected

Your HAL tester