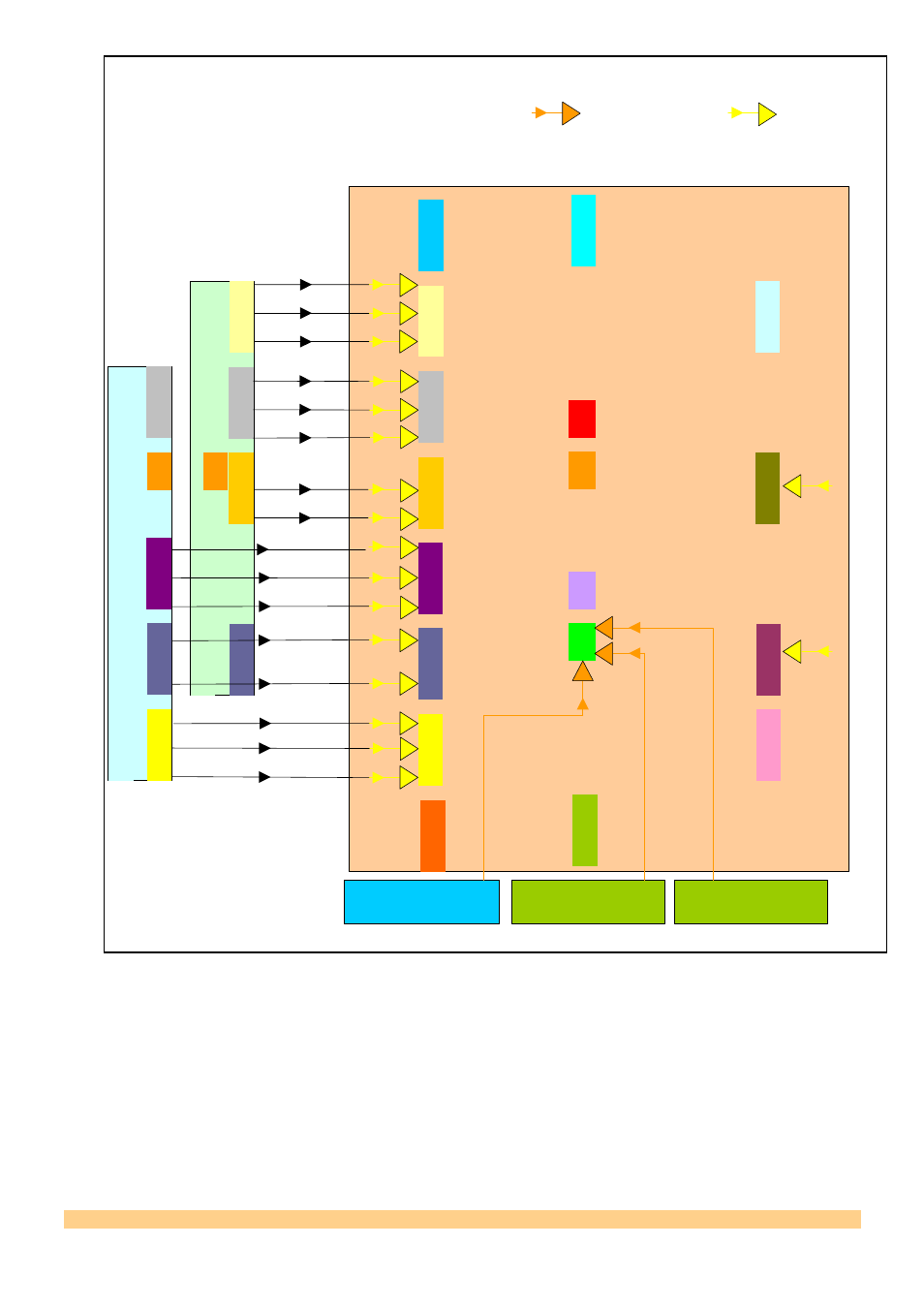

Figure 4: fpga clock buffers usage, Ban k 1 2, Left column middle column right column – Sundance SMT351T User Manual

Page 19: 125mhz differential oscillator

SMT351T User Guide

Page 19 of 37

Last Edited: 04/09/2009 11:26:00

Figure 4: FPGA clock buffers usage.

k3

1

TIM Conn

PXICLK

50Mhz single ended

osc

BA

N

K

5

BA

NK

20

BA

NK

3

BA

NK

1

BAN

K

1

2

BANK

2

BANK

4

BA

N

K

1

8

BAN

K

2

2

BA

N

K

6

BANK

1

BA

N

K

1

7

BA

N

K

1

5

BA

NK

19

DD

R2A

BA

N

K

11

BANK

1

BA

N

K

21

BA

N

K

1

7

BA

NK

13

BA

N

K

15

DDR2B

d

q

s

2

d

q

s

1

d

q

s

0

h

3

4

k

3

3

d

q

s

3

d

q

s

6

g

2

7

h

2

8

e

2

8

d

q

s

5

d

q

s

4

d

q

s

7

Regional clock input, (for single ended

clocks, or for differential clocks, P side)

d

q

s

4

d

q

s

7

d

q

s

5

d

q

s

3

d

q

s

6

a

f3

4

a

h

3

4

a

d

3

2

LEFT COLUMN

MIDDLE

COLUMN

RIGHT COLUMN

ag

21

ag

18

vc

lk

_p

os

c

5

0

Global clock input, (for single ended

clocks, or for differential clocks, P side)

d

q

s

0

d

q

s

2

d

q

s

1

d

q

s

0

pxiclk

w6

C

lko

ut

q_

p

j6

Cl

k

o

u

ti

_

p

125MHz differential

oscillator

a

k

2

6

a

k

2

9

a

k

2

8

a

a

2

9

y

2

8

m

3

1

p

3

1

BA

N

K

2

3

BA

N

K

19

BA

N

K

15

BA

N

K

1

1

BAN

K

13

BA

NK 17

BA

N

K

21

BA

N

K

25

k

3

1