Sundance SMT370v2 User Manual

Page 35

Version 2.0

Page 35 of 46

SMT370v2/v3 User Manual

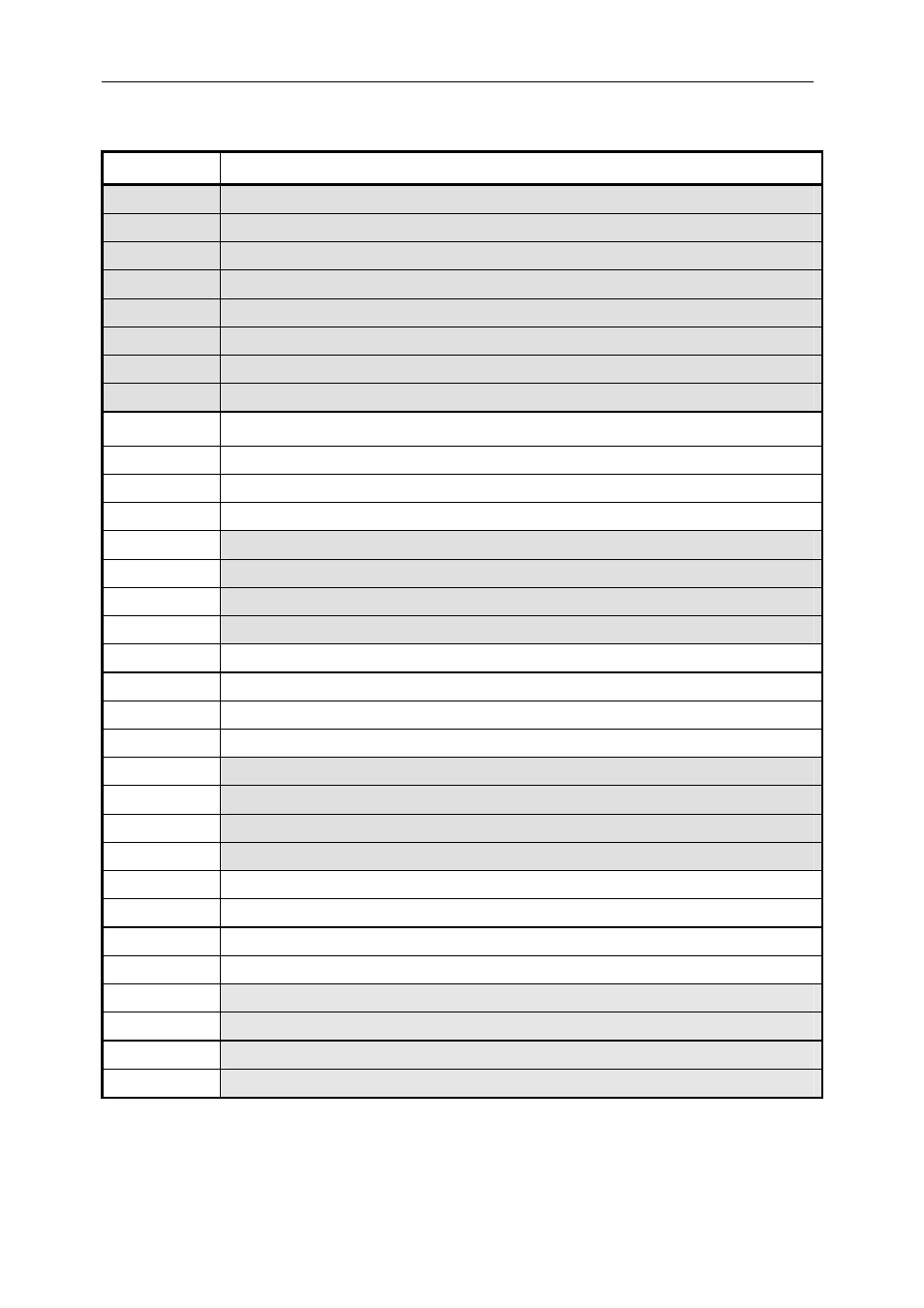

Register 0x5 – Clock management.

Bit number

Description

Bit 31

0

Bit 30

1

Bit 29

0

Bit 28

1

Bit 27

Clock Selection ADCA (ADCA - ‘0’=Internal; ‘1’=External)

Bit 26

Clock Selection ADCB (ADCB - ‘0’=Internal; ‘1’=External)

Bit 25

Clock Selection DAC (‘0’=Internal; ‘1’=External)

Bit 24

Clock Selection DAC/FPGA – must match with Bit 25 (‘0’=Internal; ‘1’=External)

Bit 23

Clock synthesizer – N (divider) Bit2 – ADCs

Bit 22

Clock synthesizer – N (divider) Bit1 – ADCs

Bit 21

Clock synthesizer – N (divider) Bit0 – ADCs

Bit 20

Clock synthesizer - M Bit8 – ADCs

Bit 19

Clock synthesizer – M Bit7 – ADCs

Bit 18

Clock synthesizer - M Bit6 – ADCs

Bit 17

Clock synthesizer - M Bit5 – ADCs

Bit 16

Clock synthesizer - M Bit4 – ADCs

Bit 15

Clock synthesizer - M Bit3 – ADCs

Bit 14

Clock synthesizer - M Bit2 – ADCs

Bit 13

Clock synthesizer - M Bit1 – ADCs

Bit 12

Clock synthesizer - M Bit0 – ADCs

Bit 11

Clock synthesizer – N (divider) Bit2 - DAC

Bit 10

Clock synthesizer – N (divider) Bit1 - DAC

Bit 9

Clock synthesizer – N (divider) Bit0 - DAC

Bit 8

Clock synthesizer - M Bit8 - DAC

Bit 7

Clock synthesizer - M Bit7 - DAC

Bit 6

Clock synthesizer - M Bit6 - DAC

Bit 5

Clock synthesizer - M Bit5 - DAC

Bit 4

Clock synthesizer - M Bit4 - DAC

Bit 3

Clock synthesizer - M Bit3 - DAC

Bit 2

Clock synthesizer - M Bit2 - DAC

Bit 1

Clock synthesizer - M Bit1 - DAC

Bit 0

Clock synthesizer - M Bit0 - DAC