Remote Processing RPC-220 User Manual

Page 12

WRITING, DEBUGGING, AND SAVING PROGRAMS

SECTION 3

Page 3-1

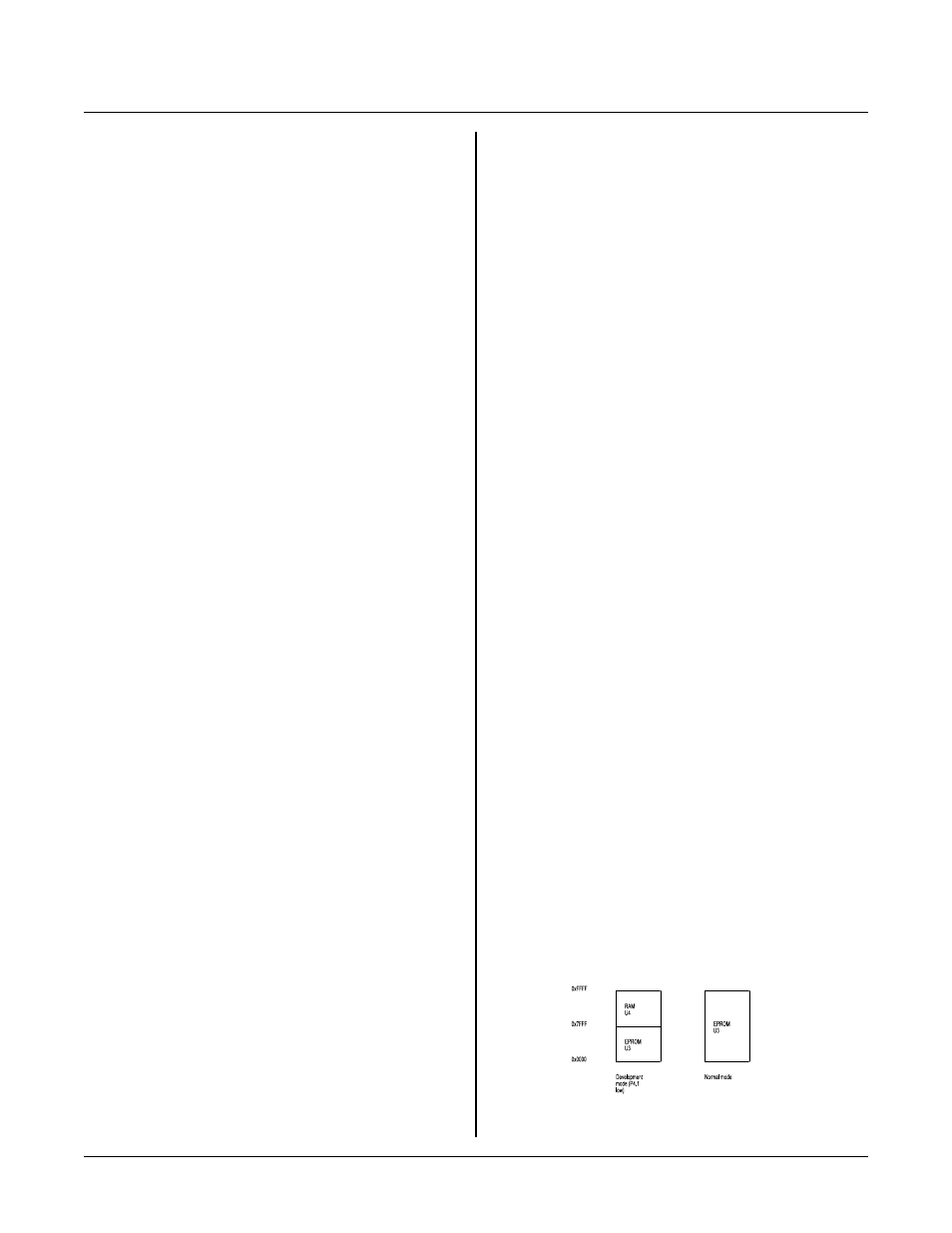

Figure 3-1 Code Memor y Map

INTRODUCTION

W R I T IN G , D E B U G G IN G A N D S A VI N G S E C T IO N 3

The RP C-220 is p rogr amm ed in C or assembly

languages. Virtually any 8051 type compiler and

assembler may be used to generate code. An assembler

is provided on the application disk. This section

provides information to set up your compiler/ assembler.

OPERATING MODES

The RPC-220 executes code in one of two modes called

development and normal. The defining difference

between the two modes is how the memory map

changes. In norm al mode, the C PU accesses its code

f r om U 3 fl a sh E P R OM e x cl us iv e ly . A l l o f RA M i n U 4

is accessed using MOVX type com mands. In

development mode, code is also accessed from RAM

starting at address 0x8000.

I/O m ode accesses devices (RTC, expansion port, and

flash EPROM ). This mode is accessed by setting the

I/O bit (CPU port P4.0) low.

During development mode (CPU port P4.1 low), RAM

from address 0x8000 to 0xffff can, but does not have to,

e x ec u te c od e . T hi s m e m or y ca n be a cc e ss ed a s I / O

using MO VX com mands.

When setting up your compiler or assem bler to develop

code, set the ORG (originate) to 8000H. The m onitor

vectors interrupts to base address + 8000H. For

example, when there is a serial interrupt the CPU

v e ct or s to a dd r e ss 0 x2 3 . T he m o ni to r h as a ju m p

instruction to address 0x8023.

When you are done w riting code, simply change the

ORG to address 0 and re-compile or assemble.

Detailed Description

Development/nor mal and I/O m odes are controlled by

two lines dir ectly from the CP U. On pow er up or reset,

these lines go high, placing the card in normal operating

mode capable of accessing external RAM. When the

DEV L line (por t P4. 1) goes low , the card is in

development mode. When the I/O line (port P4.0) goes

low, non-RAM devices are accessed. These lines are

mutually exclusive, except when pr ogram ming the flash

E P R OM .

Development mode sim ply allows CPU code to be

accessed from RAM at addresses 0x8000 to 0xffff.

MOVX type commands always access all of RAM

(assuming the I/ O control line is high). U3 flash

EPR OM is accessed as code fro m addr ess 0x0000 to

0x7fff.

The I/O contr ol line complicates things just a bit. The

purpose of this line is to allow access to non-RAM

devices (such as the real time clock and expansion

boards) while still allowing full access to RAM. The

PEE L in U6 controls R AM , I/ O, and flash acc ess. It is

designed to allow code access in the memory map

(Figur e 3-1 below ), R AM and I/O at the same time. This

is how code runs from RA M while accessing the RTC. It

also allows RAM to be modified in the code area.

Generally, the I/O control and development/normal lines

operate independen tly. T he only time both lines oper ate

together is during flash programming.

MEMORY MAPS

Memor y maps are controlled by one of two bits on the

CPU por t. Port P4. 1 controls development/normal

mode. On power up or reset, this line goes high placing

the board in normal mode. A low configures the board

for development mode.

Port P4. 0 selects between RAM and other I/O such as

the RTC, expansion port, and flash EPROM . On power

up or reset, this line goes high allowing access to RAM.

A low maps out the RAM for MO VX type instructions

only. Code c an be acce ssed if the deve lopment m ode is

selected (P4. 1 is low). W hen P4. 0 is low, the flash

eprom, expansion port, and RT C are accessible using

MOV X type comm ands.

During norm al mode, up to 64K is accessible by making

a PCB modification and replacing U3 with a 27C512

type EPROM. As delivered, 32K of code is accessible.

See Program s larger than 32K later in this section.

The mem ory map changes, depending upon the status of

the development and I/O control lines. Figure 3-1 shows

the code map during development mode.