Power-on reset circuitry, Power-on reset circuitry -4 – Altera MAX 10 Power User Manual

Page 7

Power-On Reset Circuitry

The POR circuitry keeps the MAX 10 device in the reset state until the POR monitored power supply

outputs are within the recommended operating range of the maximum power supply ramp time, t

RAMP

.

If the ramp time, t

RAMP

, is not met, the MAX 10 device I/O pins and programming registers remain tri-

stated, during which device configuration could fail.

The MAX 10 device POR circuit monitors the following power rails during power up regardless of the

power supply device options:

• V

CC

or regulated V

CC_ONE

• V

CCIO

of banks 1B and 8

(2)

• V

CCA

The POR circuitry also ensures V

CCIO

level of I/O banks 1B and 8

(2)

that contain configuration pins reach

an acceptable level before configuration is triggered.

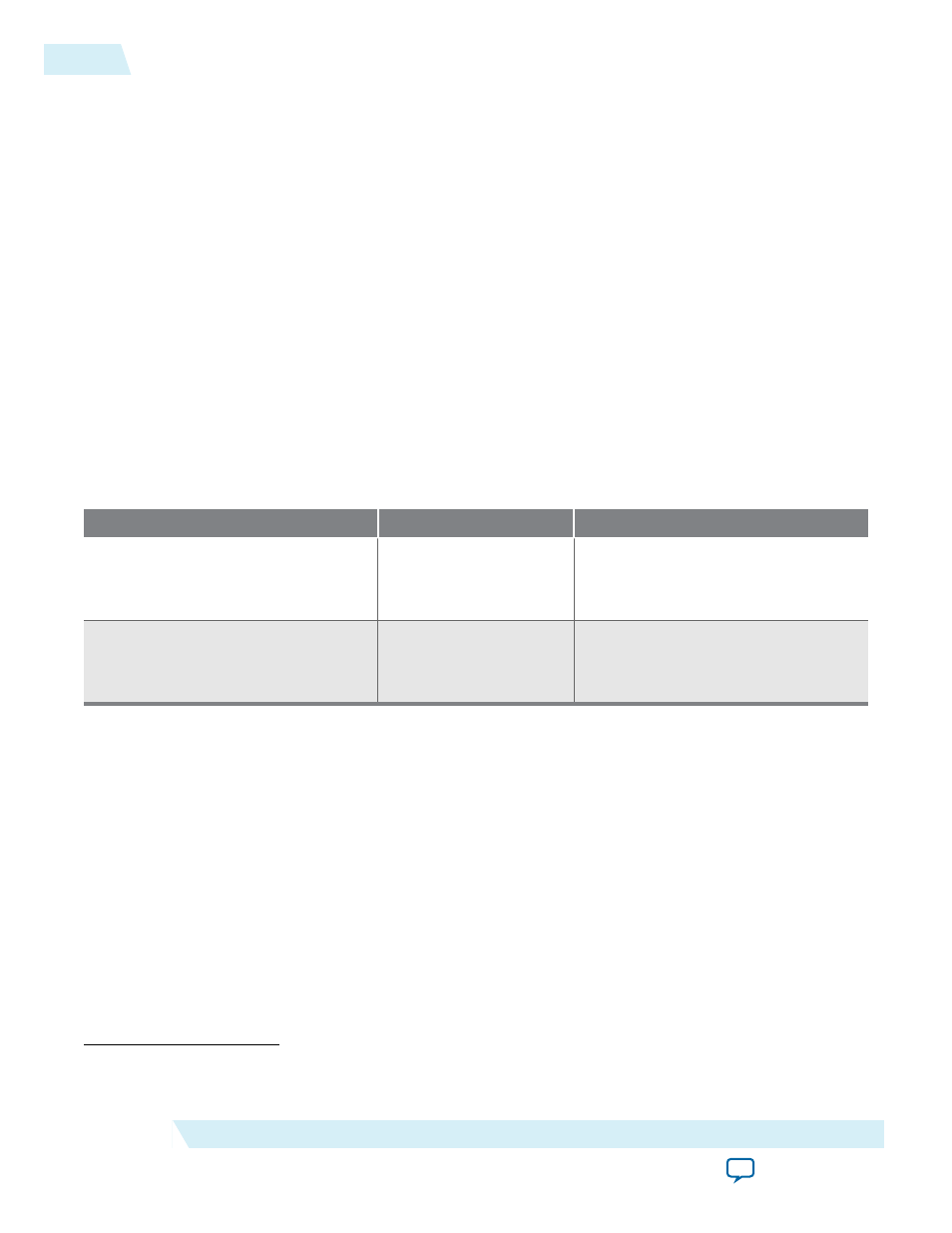

Power Supplies Monitored and Not Monitored by the POR Circuitry

Table 2-3: Power Supplies Monitored and Not Monitored by the POR Circuitry

Power Supply Device Options

Power Supplies Monitored

Power Supplies Not Monitored

Single-supply device

• Regulated V

CC_ONE

• V

CCA

• V

CCIO

(3)

—

Dual-supply device

• V

CC

• V

CCA

• V

CCIO

(3)

• V

CCD_PLL

• V

CCA_ADC

• V

CCINT

The MAX 10 POR circuitry uses an individual POR-detecting circuitry to monitor each of the configura‐

tion-related power supplies independently. The main POR circuitry is gated by the outputs of all the

individual POR detectors. The main POR circuitry waits for all individual POR circuitries to release the

POR signal before allowing the control block to start programming the device. The main POR is released

after the last ramp-up power reaches the POR trip level followed by a POR delay.

By default, Quartus

®

II assigns POR delay time to standard POR delay. For some of the applications that

need fast wake-up to begin operation, you can enable fast POR delay time on the Quartus II programmer

user interface.

(2)

V

CCIO

of banks 1 and 8 for the 10M02 device.

(3)

For banks 1B and 8 for all MAX 10 devices and banks 1 and 8 for the 10M02 device.

2-4

Power-On Reset Circuitry

UG-M10PWR

2015.02.09

Altera Corporation

MAX 10 Power Management Features and Architecture