Altera SCFIFO User Manual

Page 14

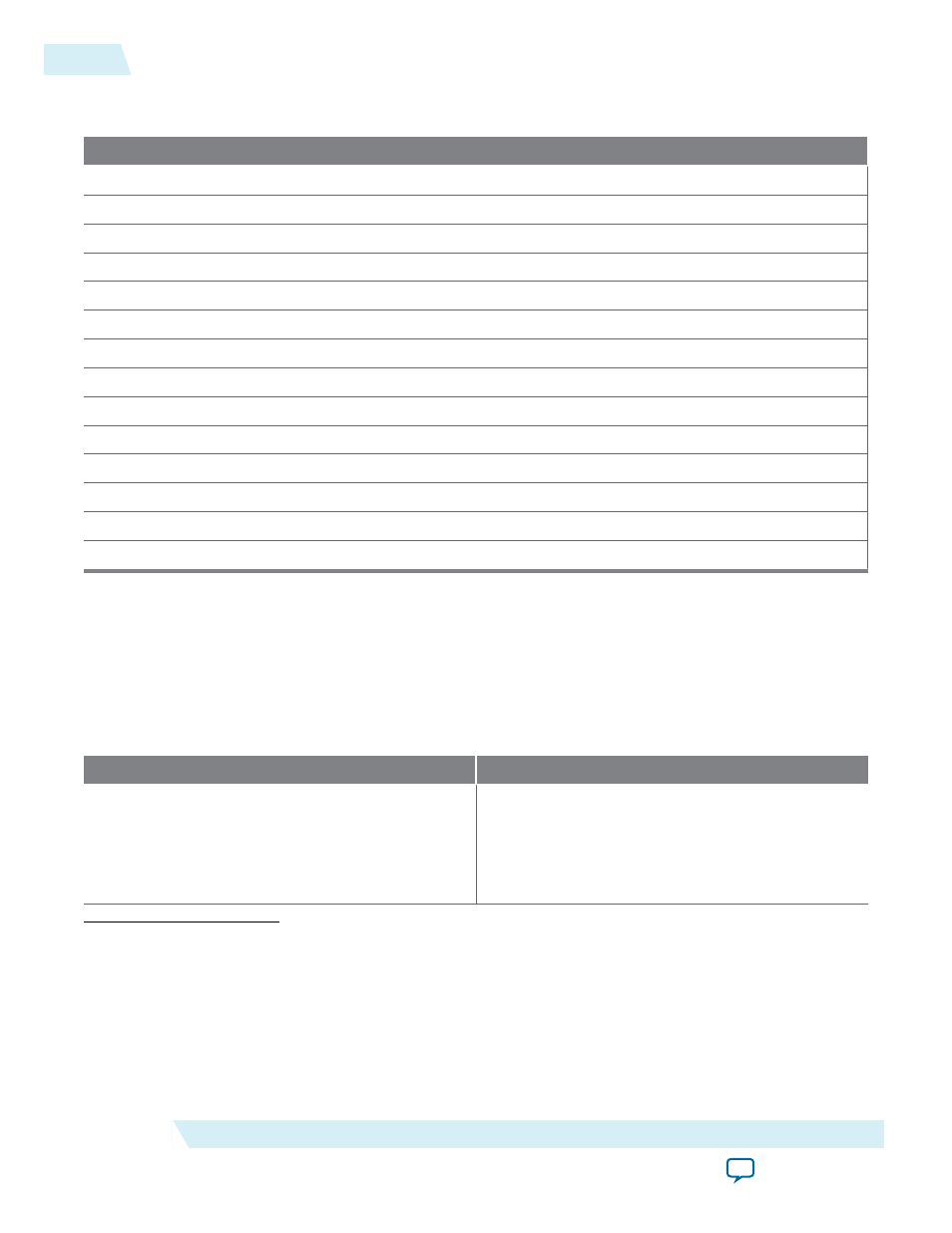

Table 6: Output Latency of the Status Flag for the DCFIFO

This table shows the output latency of the write signal (

wrreq

) and read signal (

rdreq

) for the DCFIFO.

Output Latency (in number of clock cycles)

(13)

wrreq

to

wrfull

: 1

wrclk

wrreq

to

rdfull

: 2

wrclk

cycles + following n

rdclk

wrreq

to

wrempty

: 1

wrclk

wrreq

to

rdempty

: 2

wrclk

(15)

+ following n

rdclk

(15)

wrreq

to

wrusedw[]

: 2

wrclk

wrreq

to

rdusedw[]

: 2

wrclk

+ following n + 1

rdclk

(15)

wrreq

to

q[]

: 1

wrclk

+ following 1

rdclk

(15)

rdreq

to

rdempty

: 1

rdclk

rdreq

to

wrempty

: 1

rdclk

+ following n

wrclk

(15)

rdreq

to

rfull

: 1

rdclk

rdreq

to

wrfull

: 1

rdclk

+ following n

wrclk

(15)

rdreq

to

rdusedw[]

: 2

rdclk

rdreq

to

wrusedw[]

: 1

rdclk

+ following n + 1

wrclk

(15)

rdreq

to

q[]

: 1

rdclk

SCFIFO and DCFIFO Metastability Protection and Related Options

The FIFO parameter editor provides the total latency, clock synchronization, metastability protection,

area, and f

MAX

options as a group setting for the DCFIFO.

Table 7: DCFIFO Group Setting for Latency and Related Options

This table shows the available group setting.

Group Setting

Comment

Lowest latency but requires synchronized clocks

This option uses one synchronization stage with no

metastability protection. It uses the smallest size

and provides good f

MAX

.

Select this option if the read and write clocks are

related clocks.

(13)

The output latency information is only applicable for Arria

®

GX, Stratix, and Cyclone series (except for

Stratix, Stratix GX, Hardcopy

®

Stratix, and Cyclone devices). It might not be applicable for legacy devices,

such as APEX and FLEX series of devices.

(14)

The number of n cycles for

rdclk

and

wrclk

is equivalent to the number of synchronization stages and are

related to the

WRSYNC_DELAYPIPE

and

RDSYNC_DELAYPIPE

parameters. For more information about how the

actual synchronization stage (n) is related to the parameters set for different target device, refer to

(15)

This is applied only to Show-ahead output modes. Show-ahead output mode is equivalent to setting the

LPM_SHOWAHEAD

parameter to

ON

14

SCFIFO and DCFIFO Metastability Protection and Related Options

UG-MFNALT_FIFO

2014.12.17

Altera Corporation

SCFIFO and DCFIFO IP Cores User Guide