Altera SCFIFO User Manual

Page 5

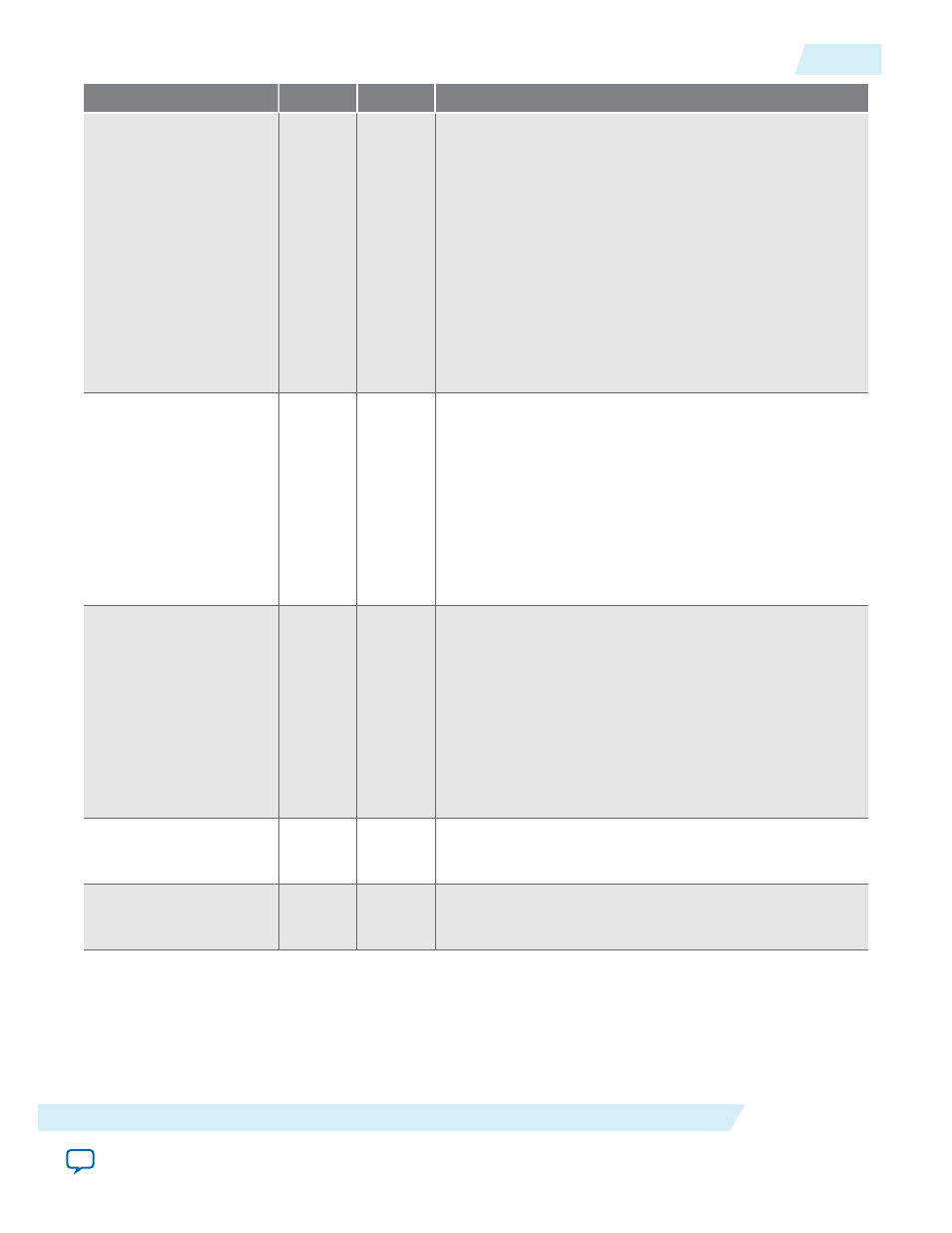

Port

Type

Required

Description

q

(3)

Output

Yes

Shows the data read from the read request operation.

For the SCFIFO IP core and DCFIFO IP core, the width

of the

q

port must be equal to the width of the

data

port.

If you manually instantiate the IP cores, ensure that the

port width is equal to the

lpm_width

parameter.

For the DCFIFO_MIXED_WIDTHS IP core, the width of

the

q

port can be different from the width of the

data

port. If you manually instantiate the IP core, ensure that

the width of the

q

port is equal to the

lpm_width_r

parameter. The IP core supports a wide write port with a

narrow read port, and vice versa. However, the width

ratio is restricted by the type of RAM block, and in

general, are in the power of 2.

full

(1)

wrfull

(2)

, (4)

rdfull

(2)

(4),

Output

No

When asserted, the FIFO IP core is considered full. Do

not perform write request operation when the FIFO IP

core is full.

In general, the

rdfull

signal is a delayed version of the

wrfull

signal. However, for Stratix III devices and later,

the

rdfull

signal function as a combinational output

instead of a derived version of the

wrfull

signal.

Therefore, you must always refer to the

wrfull

port to

ensure whether or not a valid write request operation can

be performed, regardless of the target device.

empty

(1)

wrempty

(2)

,

(4)

rdrempty

(2)

, (4)

Output

No

When asserted, the FIFO IP core is considered empty. Do

not perform read request operation when the FIFO IP

core is empty.

In general, the

wrempty

signal is a delayed version of the

rdempty

signal. However, for Stratix III devices and later,

the

wrempty

signal function as a combinational output

instead of a derived version of the

rdempty

signal.

Therefore, you must always refer to the

rdempty

port to

ensure whether or not a valid read request operation can

be performed, regardless of the target device.

almost_full

(1)

Output

No

Asserted when the

usedw

signal is greater than or equal to

the

almost_full_value

parameter. It is used as an early

indication of the

full

signal.

almost_empty

(1)

Output

No

Asserted when the

usedw

signal is less than the

almost_

empty_value

parameter. It is used as an early indication

of the

empty

signal.

UG-MFNALT_FIFO

2014.12.17

SCFIFO and DCFIFO Signals

5

SCFIFO and DCFIFO IP Cores User Guide

Altera Corporation