Altera SCFIFO User Manual

Page 17

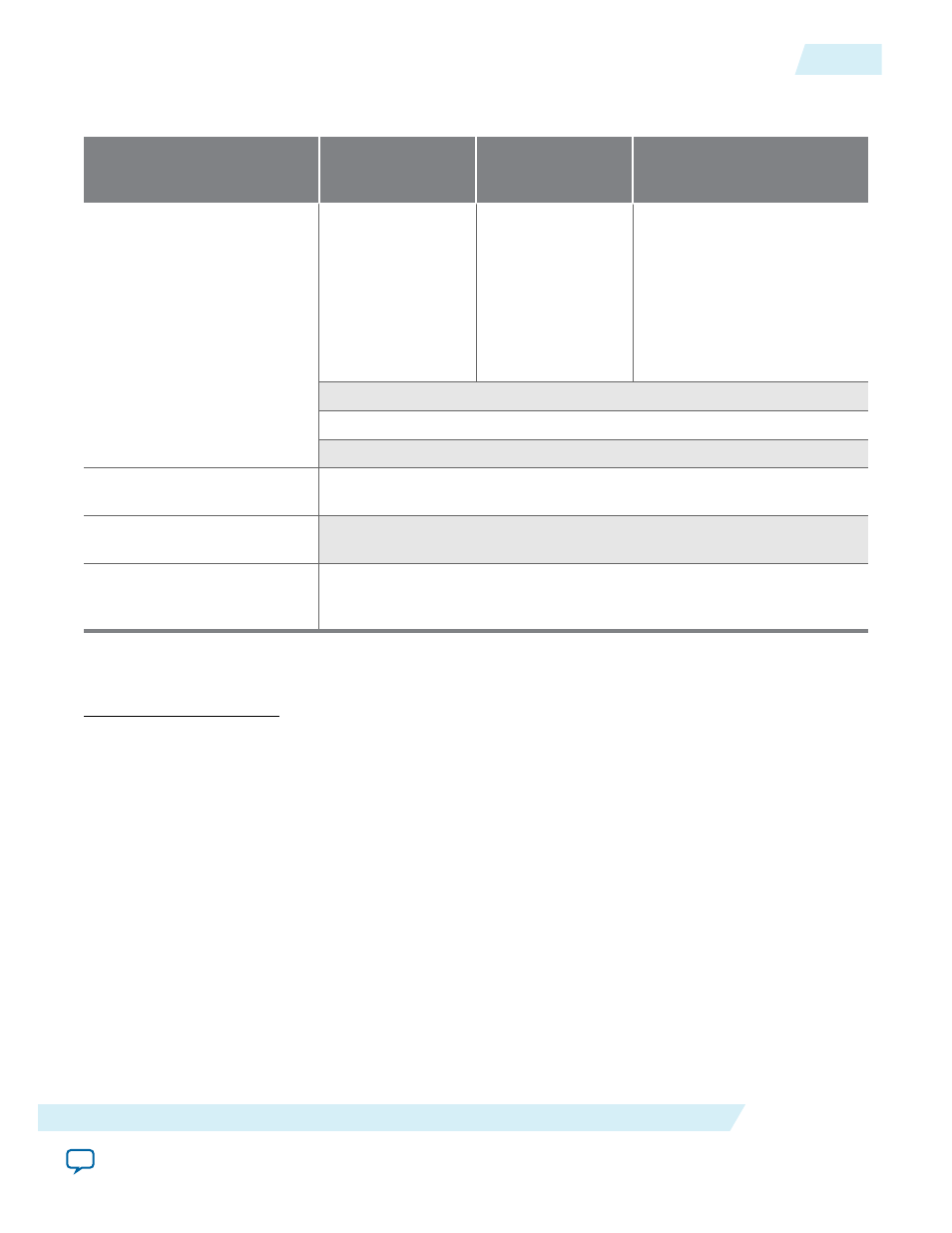

Table 10: Asynchronous Clear in DCFIFO

This table shows the asynchronous clear supported by the DCFIFO.

Mode

Asynchronous Clear

(aclr)

aclr (synchronize

with write clock)

(20)

,

(21)

aclr (synchronize with read clock)

(22)

,

(23)

Effects on status ports

Deasserts the

wrfull

signal.

The

wrfull

signal is

asserted while the

write domain is

clearing which

nominally takes

three cycles of the

write clock after the

asynchronous release

of the

aclr

input.

The

rdempty

signal is

asserted while the read

domain is clearing which

nominally takes three cycles

of the read clock after the

asynchronous release of the

aclr

input.

Deasserts the

rdfull

signal.

Asserts the

wrempty

and

rdempty

signals.

Resets the

wrusedw

and

rdusedw

flags.

Commencement of effects

upon assertion

Immediate.

Effects on the

q

output for

normal output modes

(24)

The output remains unchanged if it is not registered. If the port is

registered, it is cleared.

Effect on the

q

output for

show-ahead output

modes

(24)

The output shows 'X' if it is not registered. If the port is registered, it is

cleared.

(20)

The

wrreq

signal must be low when the DCFIFO comes out of reset (the instant when the

aclr

signal is

deasserted) at the rising edge of the write clock to avoid a race condition between write and reset. If this

condition cannot be guaranteed in your design, the

aclr

signal needs to be synchronized with the write

clock. This can be done by setting the Add circuit to synchronize 'aclr' input with 'wrclk' option from the

FIFO parameter editor, or setting the

WRITE_ACLR_SYNCH

parameter to

ON

.

(21)

Even though the

aclr

signal is synchronized with the write clock, asserting the

aclr

signal still affects all the

status flags asynchronously.

(22)

The

rdreq

signal must be low when the DCFIFO comes out of reset (the instant when the

aclr

signal is

deasserted) at the rising edge of the read clock to avoid a race condition between read and reset. If this

condition cannot be guaranteed in your design, the

aclr

signal needs to be synchronized with the read

clock. This can be done by setting the Add circuit to synchronize 'aclr' input with 'rdclk' option from the

FIFO parameter editor, or setting the

READ_ACLR_SYNCH

parameter to

ON

.

(23)

Even though the

aclr

signal is synchronized with the read clock, asserting the

aclr

signal affects all the

status flags asynchronously.

(24)

For Stratix and Cyclone series (except Stratix, Stratix GX, and Cyclone devices), the DCFIFO only supports

registered

q

output in Normal mode, and unregistered

q

output in Show-ahead mode. For other devices, you

have an option to register or unregister the

q

output (regardless of the Normal mode or Show-ahead mode)

in the FIFO parameter editor or set through the ADD_RAM_OUTPUT_REGISTER parameter.

UG-MFNALT_FIFO

2014.12.17

SCFIFO and DCFIFO Synchronous Clear and Asynchronous Clear Effect

17

SCFIFO and DCFIFO IP Cores User Guide

Altera Corporation