Verifying avalon-mm master dut, Setting up the test, Creating an sopc builder testbench for the dut – Altera Avalon Verification IP Suite User Manual

Page 163: Verifying avalon-mm master dut –7, Setting up the test –7, Creating an sopc builder testbench for the dut –7

Chapter 1: SOPC Builder Tutorial

1–7

Verifying Avalon-MM Master DUT

May 2011

Altera Corporation

Avalon Verification IP Suite User Guide

Verifying Avalon-MM Master DUT

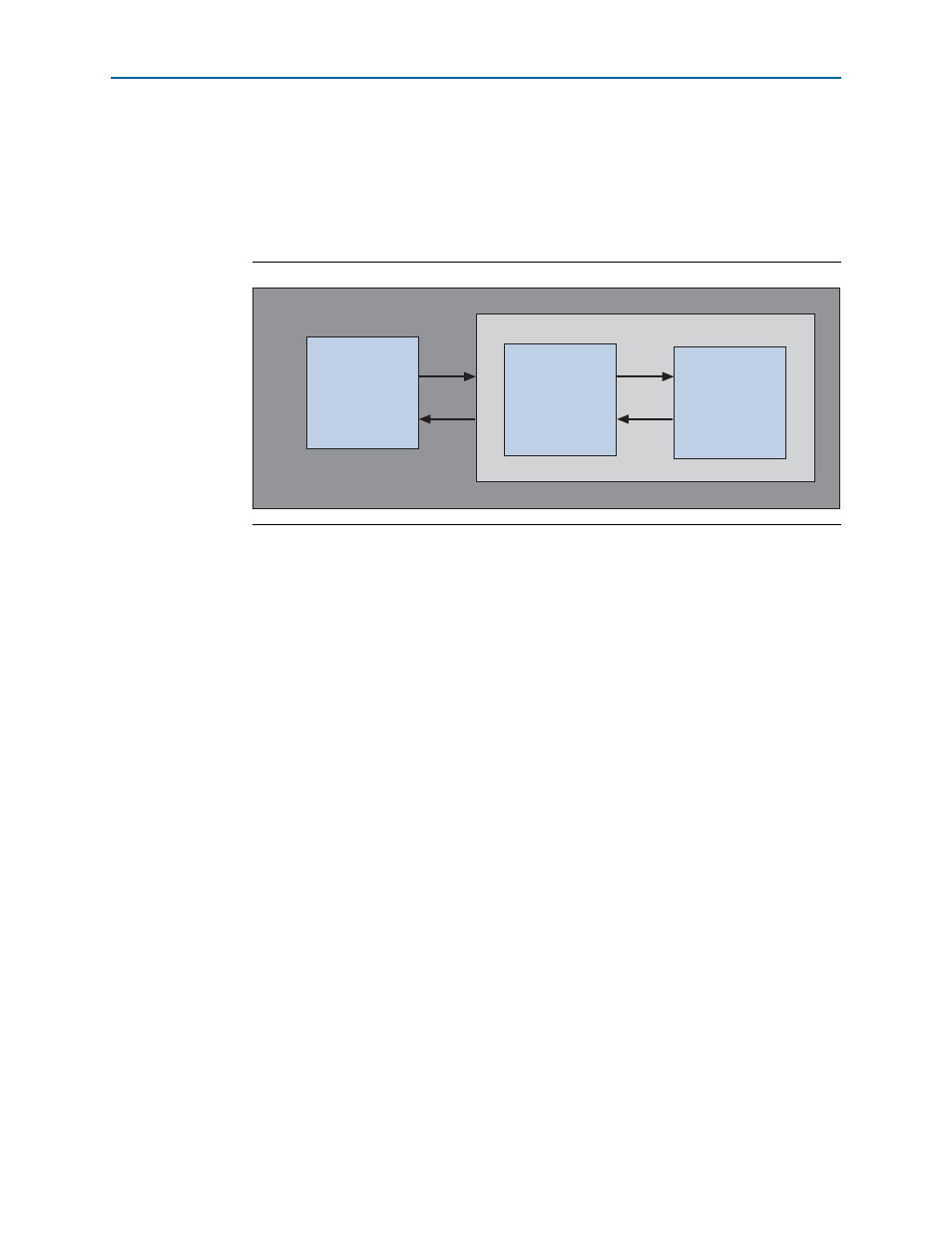

illustrates the top-level testbench to verify an Avalon-MM master

component using an Avalon-MM Slave BFM. The Avalon-MM master DUT is a simple

write-read master that writes data to a slave component and reads back the data

written.

The amount of data written is specified by the master’s

BLOCKSIZE

parameter. The

default value for this parameter is 4. When all data is written, the master DUT reads

the data back from the slave BFM and checks it against the expected data. If a

mismatch occurs, the master DUT asserts its exported

error

signal.

The Avalon-MM Slave BFM component responds to the master’s commands when

the

signal_command_received

event is triggered. The test program removes the

master command out of the slave BFM component’s client command queue. If the

command is a write, the write data is saved to a local array. For read commands, data

is read out of the local array. The test program then constructs a response descriptor

with the read data. The slave BFM drives the response to the master DUT. The test

ends after the master DUT has received all responses from the slave BFM. The test

passes if the master DUT does not assert its

error

signal.

f

For more information on the methods used by the Avalon-MM Slave BFM to construct

commands, refer to the

“Application Program Interface” on page 3–10

of the Avalon

Memory-Mapped Slave BFM.

Setting Up the Test

This section describes the steps to build a test system in the SOPC Builder to verify the

Avalon-MM master using the Avalon-MM Slave BFM.

Creating an SOPC Builder Testbench for the DUT

Before you run the design file, unzip the ug_avalon_verification.zip file to a working

directory on your hard drive. This location is referred to as

<working_directory>

.

To create an SOPC Builder testbench, follow these steps:

Figure 1–3. Top-Level Testbench for Avalon-MM Master Component

Avalon-MM

Master

Avalon-MM

Slave

BFM

SOPC Builder

Top-level File

Test

Program