Avalon-mm master bfm, Functional description, Chapter 1. avalon-mm master bfm – Altera Avalon Verification IP Suite User Manual

Page 24: Functional description –1, Chapter 1, avalon-mm master bfm

May 2011

Altera Corporation

Avalon Verification IP Suite User Guide

1. Avalon-MM Master BFM

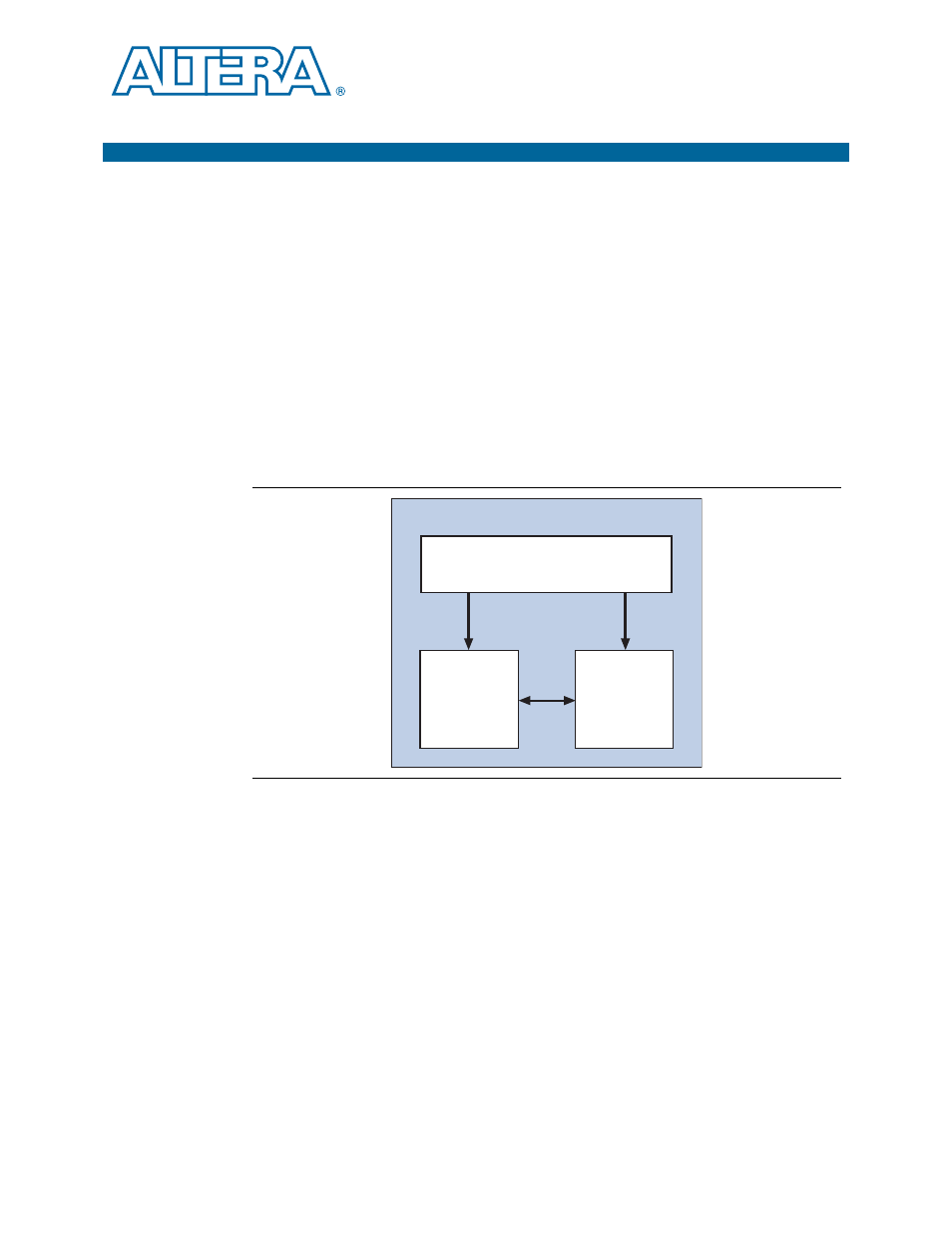

The Avalon-MM Master BFM implements the Avalon-MM interface protocol,

including: read, write, burst read, and burst write.

shows the top-level

modules for a typical testbench that uses the Avalon-MM BFM to verify an

Avalon-MM slave component. In addition to the Altera-provided Avalon-MM Master

BFM component, the typical testbench includes a test program and the DUT that

includes an Avalon-MM slave interface. The Altera-provided Avalon-MM BFM

highlights any misinterpretation of the protocol implemented by the DUT that might

be missed in a testbench designed by a single engineer.

1

The BFMs allow illegal transactions so that you can test the error-handling

functionality of your DUT; consequently, the BFMs cannot be relied upon to guarantee

protocol compliance. The Avalon Monitors components verify protocol compliance.

f

For more information about the Avalon-MM specification supported in SOPC Builder,

refer to the

.

f

For more information about the Avalon-MM specification supported in Qsys, refer to

Functional Description

This section provides a functional description of the Avalon-MM Master BFM. It

includes the following topics:

■

■

Figure 1–1. Top-Level Module to Verify an Avalon-MM Slave Device

Avalon-MM

Master BFM

Avalon-MM

Slave Component

DUT

Testbench

Avalon-MM

Test Program

HDL

HDL