Qsys tutorial, Software requirements, Verifying avalon-st dut – Altera Avalon Verification IP Suite User Manual

Page 168: Chapter 2. q, Software requirements –1 verifying

May 2011

Altera Corporation

Avalon Verification IP Suite User Guide

2. Qsys Tutorial

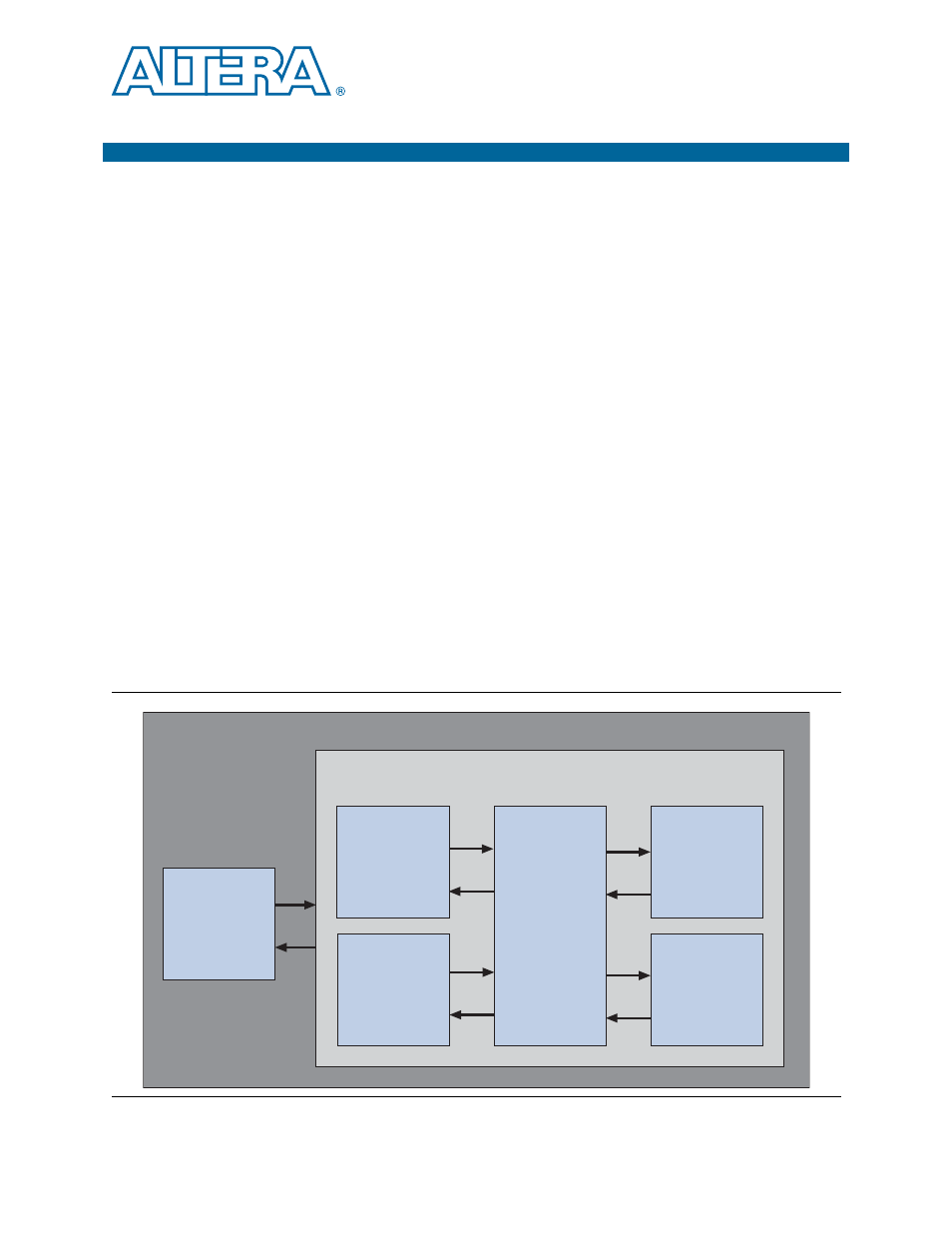

This chapter demonstrates how to use the Avalon-ST Source and Sink BFMs to verify

the functionality of an Avalon-ST component using a Qsys-generated testbench. In

this example, the Avalon-ST Single-Clock FIFO buffer is the DUT. The testbench

includes both the Avalon-ST Source and Sink BFMs to verify the DUT behavior.

Software Requirements

The following software and file are required to run the test:

■

Quartus II software, version 11.0 or later.

■

ModelSim-AE software that you installed with the Quartus II software.

■

The ug_avalon_verification.zip file. This design example file is available for

.

Verifying Avalon-ST DUT

shows the test setup to verify the Avalon-ST Single-Clock FIFO buffer

using the Avalon-ST Source and Sink BFMs. The Avalon Clock Source and Reset

Source BFMs provide clock and reset functionalities to the DUT. The Avalon-ST

Source BFM connects to the DUT and drives transactions. The Avalon-ST Sink BFM

monitors transactions from the Avalon-ST Single-Clock FIFO buffer. The test program

controls the BFMs using the BFM API to drive and monitor transactions.

Figure 2–1. Top-Level Testbench for Avalon-ST DUT Component

Qsys Generated Testbench

Top-level File

Test

Program

Avalon-ST

Single-Clock

FIFO Buffer

(DUT)

Avalon Clock

Source BFM

Avalon-ST

Source BFM

Avalon-ST

Sink BFM

Avalon Reset

Source BFM