Altera Low Latency 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 129

Address

Name

Bit

Description

HW Reset

Value

Access

0x407

MAX_TX_SIZE_

CONFIG

[15:0]

Maximum size of Ethernet frames for

CNTR_

TX_OVERSIZE

.

If the IP core transmits an Ethernet frame of

size greater than the number of bytes specified

in this register, and the IP core includes TX

statistics registers, the IP core increments the

64-bit

CNTR_TX_OVERSIZE

register.

9600

(decimal)

RW

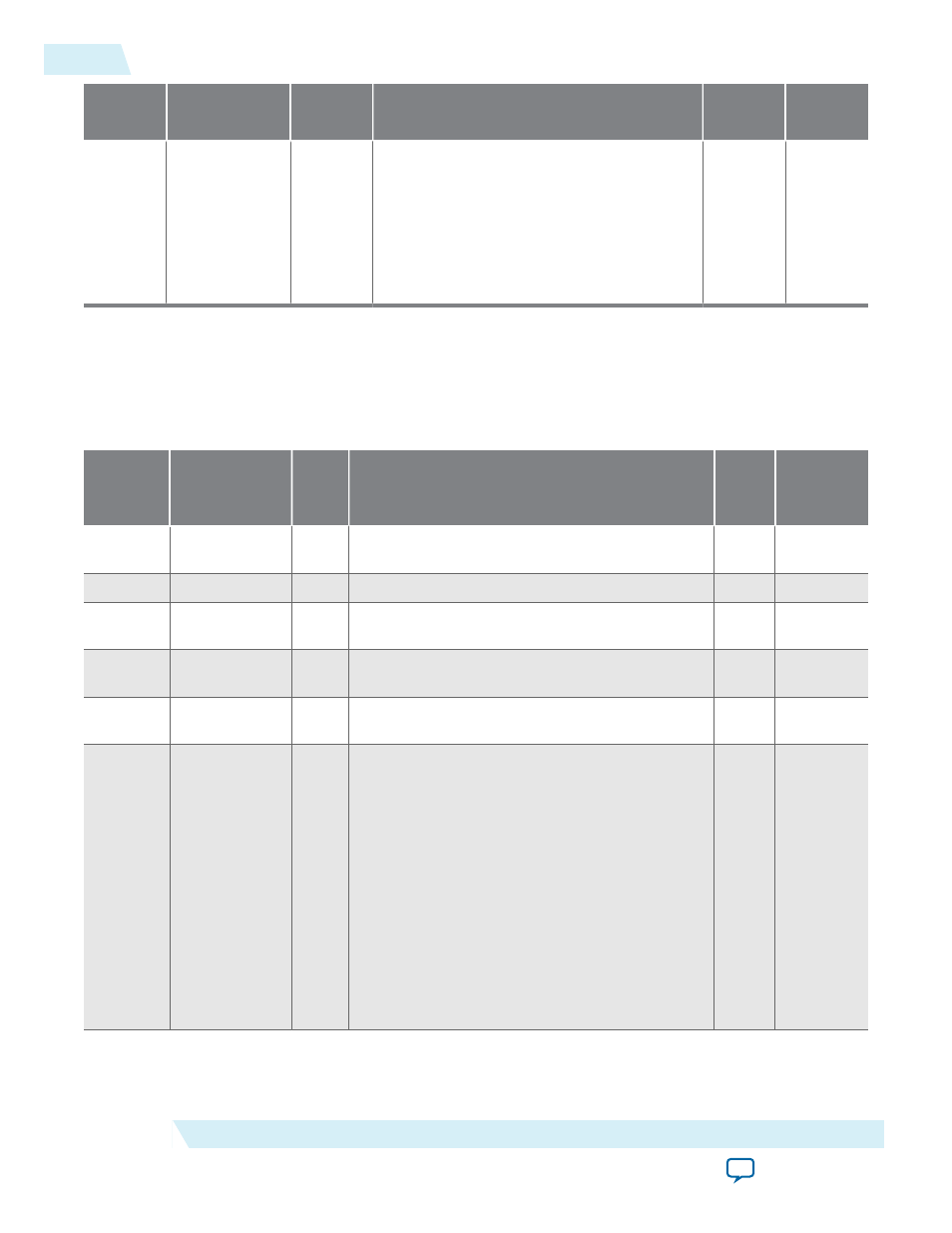

Table 3-25: RX MAC Configuration Registers

This table documents the non-fault link signaling registers in the RX MAC address space. The local and remote

fault status register at address 0x508 is documented with the link fault signaling registers. The local and remote

fault status register is available only if you turn on Enable link fault generation in the Low Latency 40-100GbE

parameter editor.

Address

Name

Bit

Description

HW

Reset

Value

Access

0x500

RXMAC_REVID

[31:0] RX MAC revision ID.

0x0206

2015

RO

0x501

RXMAC_SCRATCH

[31:0] Scratch register available for testing.

32'b0

RW

0x502

RXMAC_NAME_0

[31:0] First 4 characters of IP core variation identifier

string "40gMACRxCSR" or "100gMACRxCSR".

RO

0x503

RXMAC_NAME_1

[31:0] Next 4 characters of IP core variation identifier

string "40gMACRxCSR" or "100gMACRxCSR".

RO

0x504

RXMAC_NAME_2

[31:0] Final 4 characters of IP core variation identifier

string "40gMACRxCSR" or "100gMACRxCSR".

RO

0x506

MAX_RX_SIZE_

CONFIG

[15:0] Maximum size of Ethernet frames for

CNTR_RX_

OVERSIZE

and for

rx_error[3]

or

l<n>_rx_

error[3]

and for .the

RxOctetsOK

register.

If the IP core receives an Ethernet frame of size

greater than the number of bytes specified in this

register, and the IP core includes RX statistics

registers, the IP core increments the 64-bit

CNTR_

RX_OVERSIZE

register.

An Ethernet frame of size greater than the number

of bytes specified in this register is considered

oversized and therefore does not contribute to the

value in the

RxOctetsOK

register.and does cause the

assertion of

rx_error[3]

or

l<n>_rx_error[3]

.

9600

(decim

al)

RW

3-84

Low Latency 40-100GbE IP Core MAC Configuration Registers

UG-01172

2015.05.04

Altera Corporation

Functional Description