Altera Low Latency 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 157

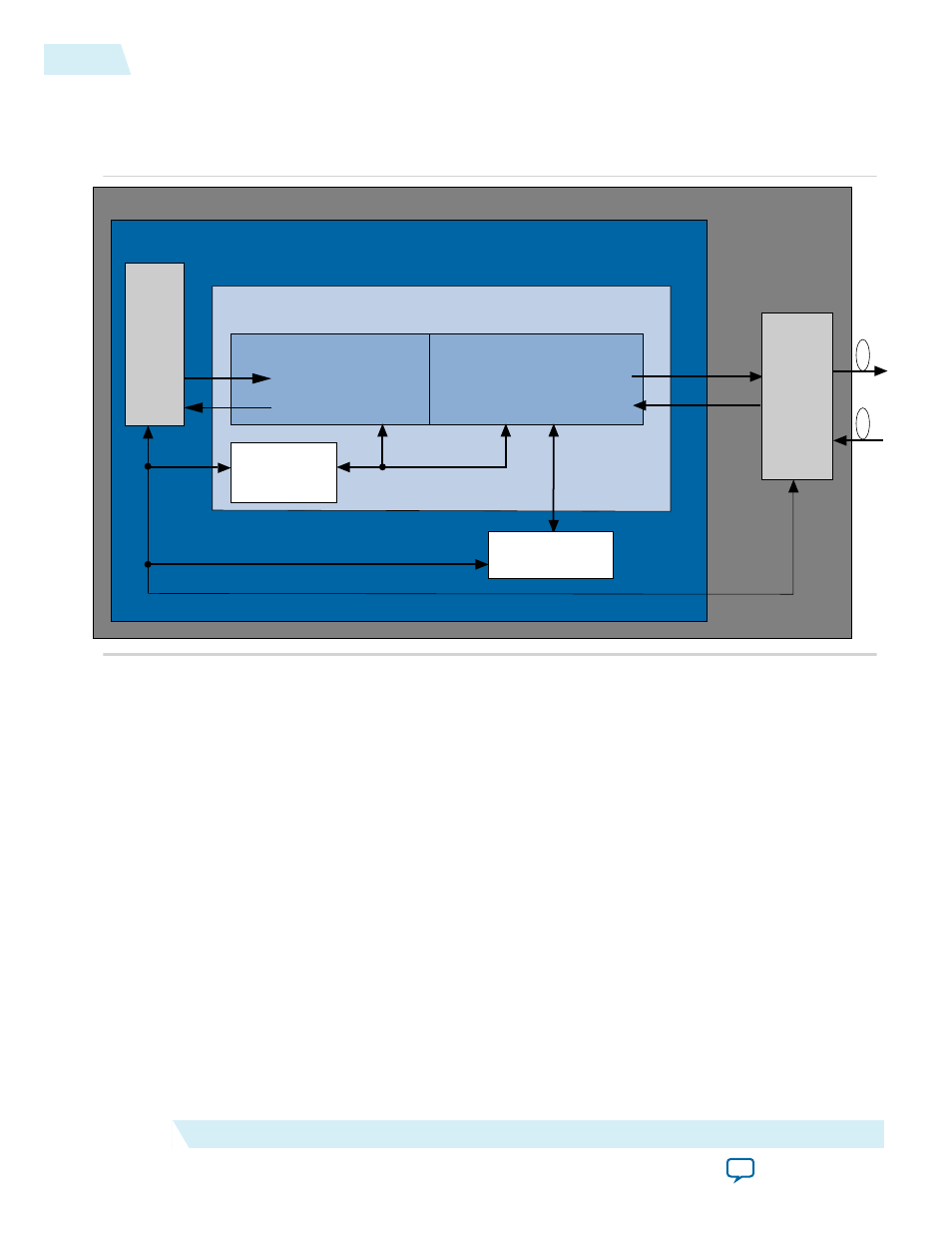

Figure A-3: High Level Block Diagram for the Stratix V 40-100GbE Example Project

The example project for Stratix V variations includes a reconfiguration controller to support dynamic

reconfiguration of the device transceivers, as well as client logic to exercise the IP core.

Low latency 40- or 100-Gbps Ethernet MAC and PHY IP Core

Low Latency 40- or 100-Gbps Ethernet Example Project for Stratix V IP Core Variations

Altera FPGA

TX

FIFO

MAC

Transceiver PHY

Avalon-ST

Avalon-ST

Control and

Status Interface

Avalon-MM

Reconfiguration

Controller

Client

Logic

PMD

Optical

Module

CFP

or

QSFP

The example projects for all IP core variations with Enable 1588 PTP turned on include a time-of-day

module connected to the IP core as required.

Altera’s example project includes either the 40GbE or 100GbE IP core. In the example project for Arria 10

IP core variations, one or two ATX PLLs connect to the TX and RX Ethernet MAC, depending on the IP

core variation.

Related Information

For more information about the Avalon-MM and Avalon-ST protocols, including timing diagrams.

Information about the correspondence between PLLs and transceiver channels in the Arria 10

transceivers, and information about how to configure an external PLL for your own design.

Generating the Low Latency 40-100GbE Example Project

A-4

Generating the Low Latency 40-100GbE Example Project

UG-01172

2015.05.04

Altera Corporation

Low Latency 40-100GbE IP Core Example Project