Maps and registers – Artesyn ATCA-7480 Installation and Use (February 2015) User Manual

Page 126

Maps and Registers

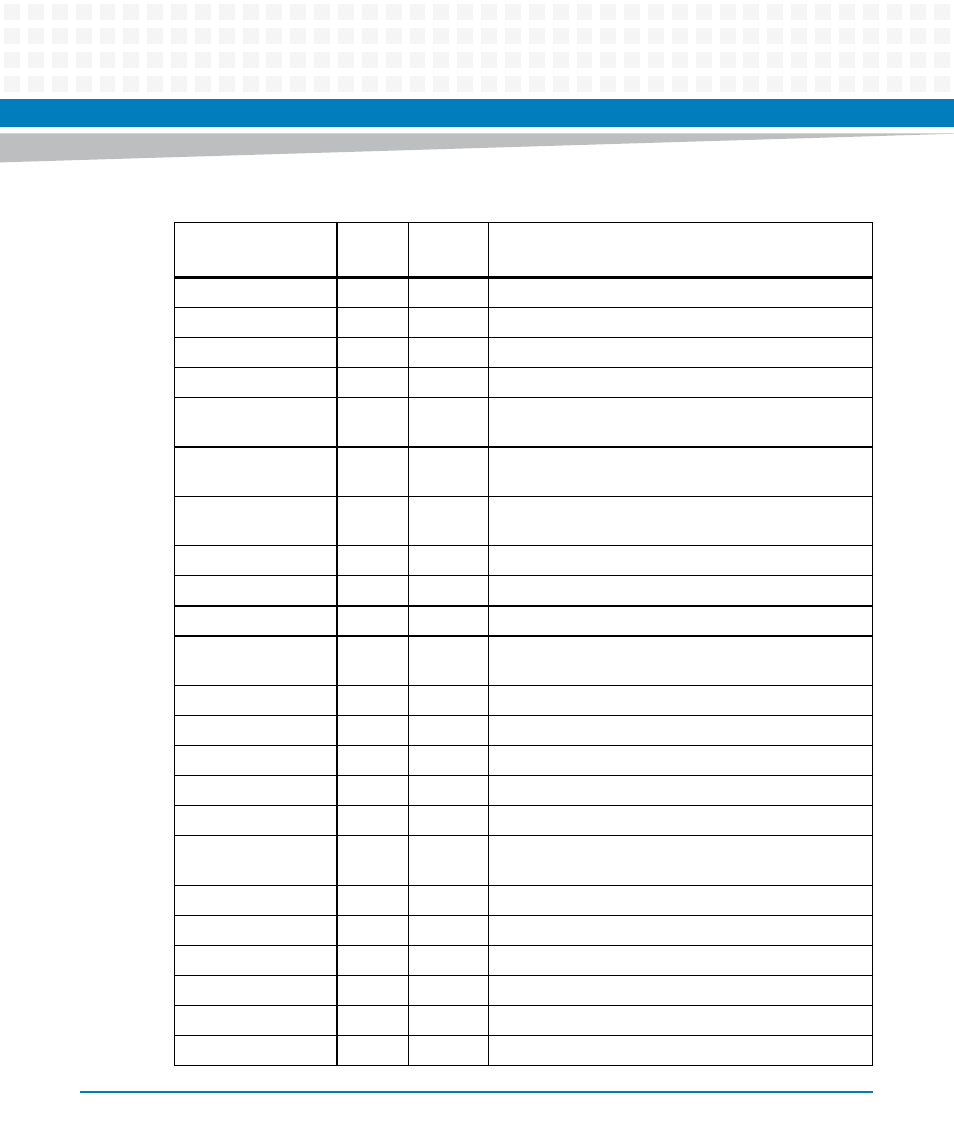

ATCA-7480 Installation and Use (6806800T17A)

126

0x07

r

r/w

IPMC Power Level Multiplier Register

0x08

-

r

ME Power Failure State Register (See,

0x09

-

r

ME Power Failure Cause Register (See,

)

0x0A

-

r

Payload Power Failure State Register (See,

0x0B

-

r

Payload Power Failure Cause Register 1 (See,

0x0C

-

r

Payload Power Failure Cause Register 2 (See,

0x0D

-

r

Payload Power Failure Cause Register 3 (See,

0x0E

-

r

Power Status Register (See,

)

0x10

r/w1c

r

BIOS Reset Source Register (See,

)

0x11

r/w

r

Reset Mask Register (See,

)

0x12

r/w1c

r

BIOS IPMC Watchdog Timeout Register (See,

0x13

w

-

BIOS Push Button Enable Register (See,

0x14

r/w1c

r

OS Reset Source Register (See,

)

0x15

r/w1c

r

OS IPMC Watchdog Timeout Register (See,

0x16

-

r/w

IPMC Watchdog Timeout Register (See,

)

0x17

-

r/w1c

IPMC Reset Source Register (See,

0x18

r/w

r

DIMM ADR Feature Configuration Register (See,

0x19

-

r/w1c

IPMC Interrupt Status Register (See,

0x1A

r/w1c

r

DIMM ADR Status Register (See,

0x1E

-

w

CPU Control Register (See,

0x1F

-

w

S-States Control Register (See,

0x20

-

w

NMI Generation Register (See,

0x20

r/w1c

-

NMI Interrupt Status Register (See,

Table 5-38 FPGA Register Map Overview (continued)

LPC Address Offset

LPC I/O

IPMC I2C

Description