1 nmi generation register, 2 nmi interrupt status register, 16 interrupt control and status registers – Artesyn ATCA-7480 Installation and Use (February 2015) User Manual

Page 150: Table 5-66, Nmi generation register, Table 5-67, Nmi interrupt status register, Maps and registers

Maps and Registers

ATCA-7480 Installation and Use (6806800T17A)

150

5.1.15.1 NMI Generation Register

IPMC can initiate a NMI high pulse writing 0xA5 to this register. The minimum pulse width of

the NMI is 175μs.

5.1.15.2 NMI Interrupt Status Register

When the IPMC has generated a NMI pulse, the host can identify this event reading the register

below. The host needs to clear this flag.

5.1.16 Interrupt Control and Status Registers

The interrupt status registers indicate events of the interrupt input signals. When an interrupt

event occurred, the corresponding status bit is read 1. Writing 1 of the corresponding bit clears

the bit.

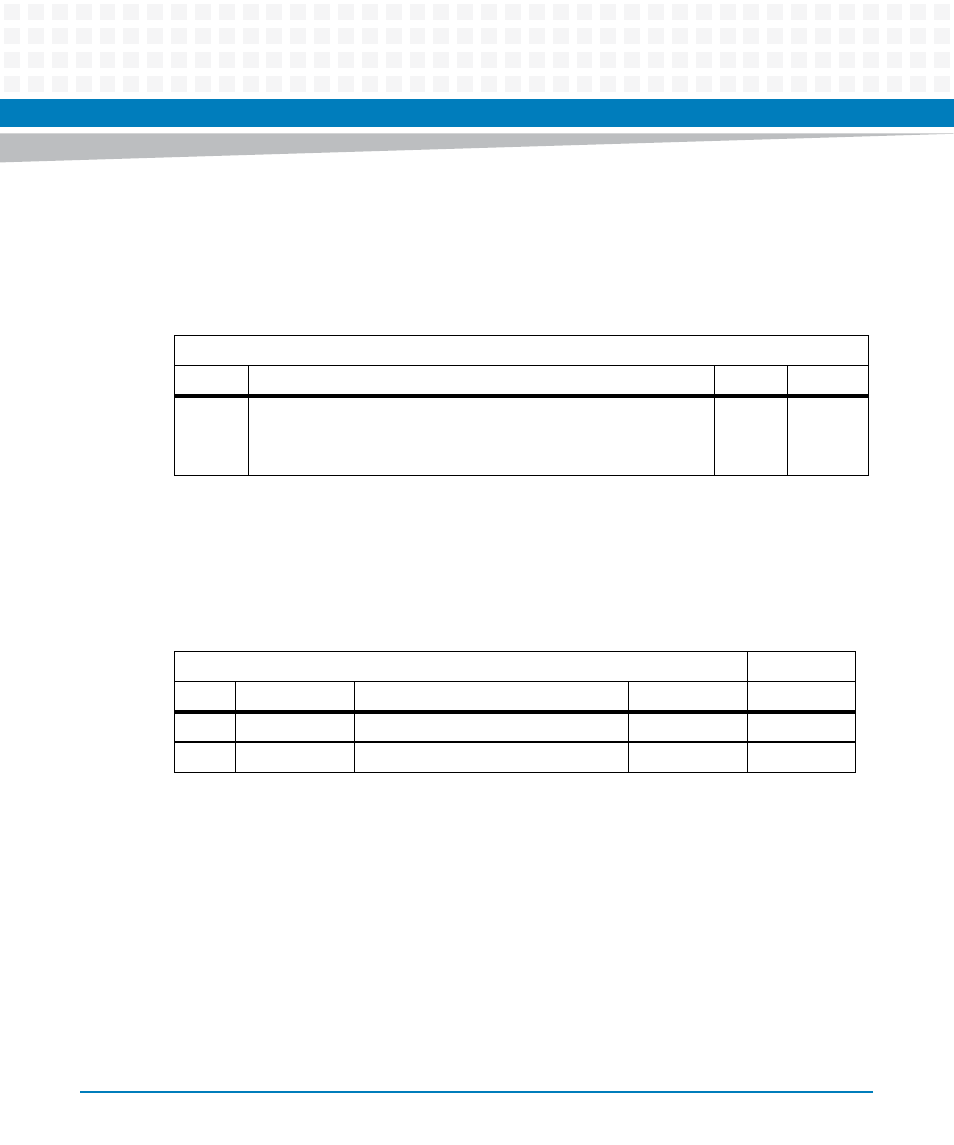

Table 5-66 NMI Generation Register

Address Offset: 0x20

Bit

Description

Default

Access

7:0

NMI pulse generation. Minimum pulse width is 175μs:

0xA5: Generate NMI pulse

all other values are ignored

-

IPMC: w

Table 5-67 NMI Interrupt Status Register

Address Offset: 0x20

Bit

Signal/Group

Description

Default

Access

0

PCH_NMI

NMI pulse triggered by IPMC.

PWR_GOOD: 0 LPC: r/1wc

7:1

-

Reserved

0

r