Maximum period difference logic, Measured frequency converter, Frequency comparator logic – Basler Electric BE1-81O/U User Manual

Page 15: Definite time delay logic

9137300990 Rev N

9

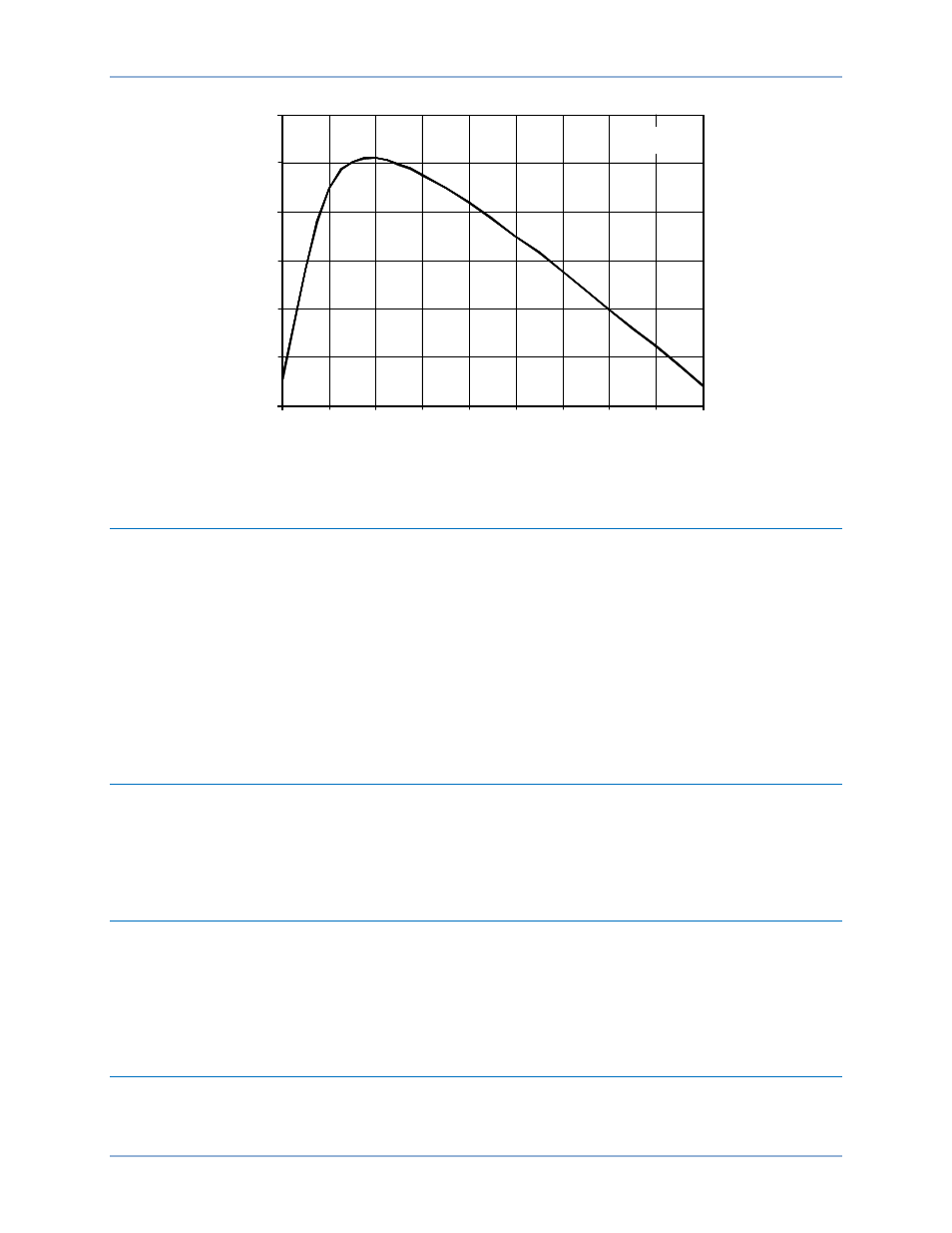

Figure 5. Band-Pass Filter Characteristics

Maximum Period Difference Logic

This logic includes an address resister and programmable, read-only memory (PROM). Following the

EOPR pulse from the minimum period difference logic, the address register counts 1 MHz clock pulses to

address 4,096 data words stored in the PROM. Completion of the count represents the period of the 30

Hz minimum detectable frequency limit. If zero-cross pulses have properly occurred before the count

ends, the measured frequency converter computes the actual frequency, within the frequency limits,

utilizing the corresponding data words stored in the PROM.

If sensed frequency decreases to less than the 30 Hz minimum frequency limit (zero-cross pulses occur

after the counts are completed) for three consecutive cycles, the measured frequency converter

computes the frequency at the minimum frequency limit. The definite time delay is not affected by the

frequency limit being exceeded.

Measured Frequency Converter

The measured frequency converter changes the data word from the maximum period difference logic to a

four-digit, binary-coded decimal (BCD) number that represents the actual sensed frequency (with an

accuracy of 0.01 Hz) within the 30 to 80 Hz limits. The BCD frequency data bus passes this data to the

frequency comparator logic of each setpoint.

Frequency Comparator Logic

This logic compares the BCD number representing the actual sensed frequency with the Frequency

Selector Switch setting on the front panel. An output is triggered when the sensed frequency decreases

below the setpoint (Over/Under Selector Switch set to U), or when the sensed frequency increases above

the setpoint (Over/Under Selector Switch set to O). The resultant output consists of an enabling level that

starts a count-up timer and lights the front panel Pickup Indicator.

Definite Time Delay Logic

The enable signal (representing a detected over or underfrequency condition) from the frequency

comparator logic initiates the count of zero-cross pulses. After three consecutive cycles exceed the

pickup setting, the definite time delay logic lights the Pickup Indicator. When the front-panel Time Delay

Frequency (HZ)

dB

12

13

14

15

16

17

18

12

40

60

80

100

120

140

160

180

200

D2856-24

BE1-81O/U

Functional Description