Timing analysis – Altera GPIO User Manual

Page 16

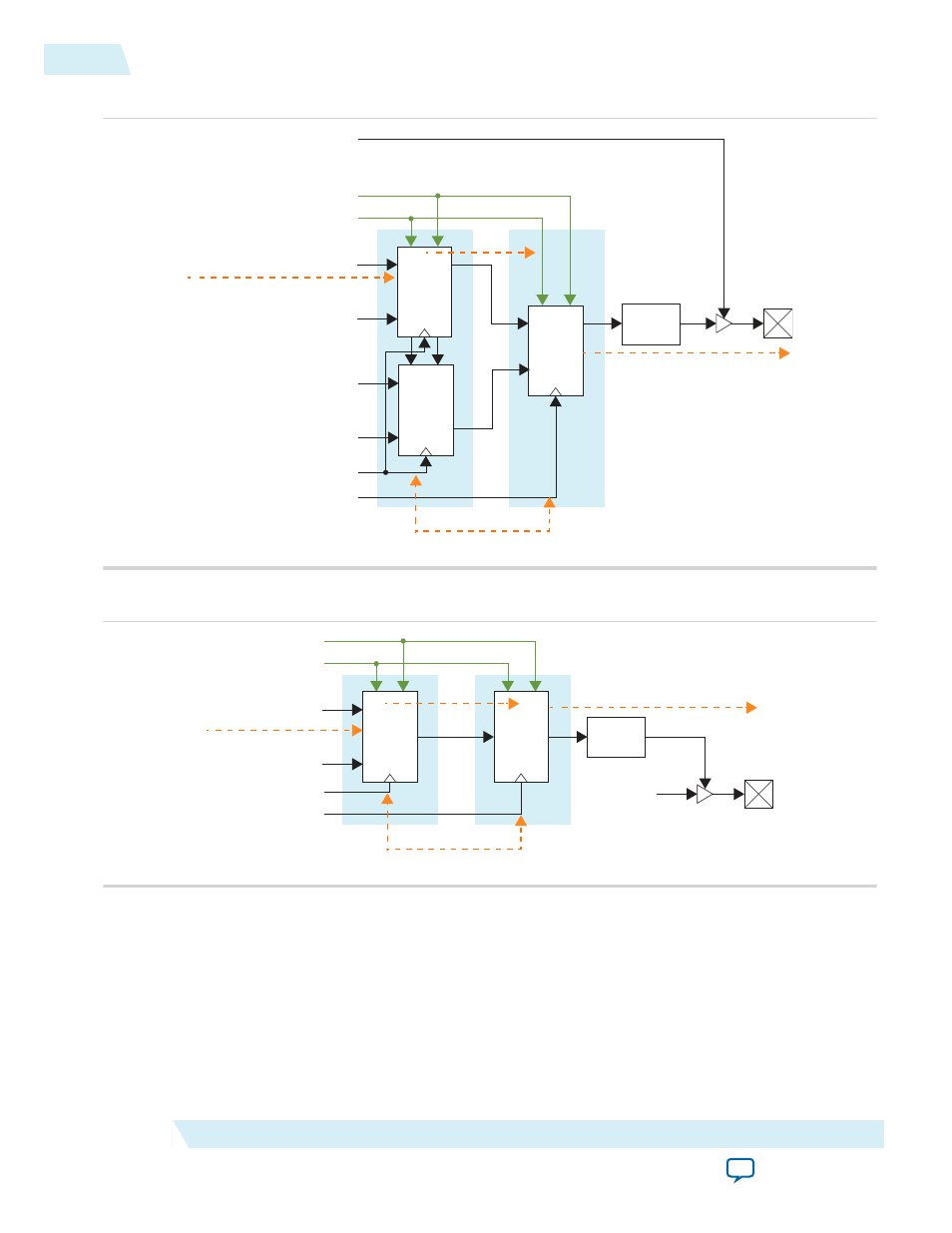

Figure 9: Timing Components in the Altera GPIO Output Path

PAD

ACLR_N

APRE_N

DATAOUT[0]

DATAOUT[2]

DATAOUT[1]

DATAOUT[3]

CLK_HR

CLK_FR

DDIO

OUT

DDIO

OUT

DDIO

OUT

Delay

Element

HR

FR

OE

from Output

Enable Path

Half-rate/Full-rate Transfer Path

I/O Path

Core Interface Clock Path

Core Interface Data Path

Figure 10: Timing Components in the Altera GPIO Output Enable Path

ACLR_N

APRE_N

OEIN[0]

OEIN[1]

CLK_HR

CLK_FR

DDIO

OUT

FF

Delay

Element

HR

FR

From Output

Data Path

Half-rate/Full-rate Transfer Path

Core Interface Data Path

Core Interface Clock Path

I/O Path

Timing Analysis

The Quartus II software does not automatically generate the SDC timing constraints for Altera GPIO IP

core. You must manually enter the timing constraints. This section provides simple instructions and

examples on how to timing constrain the Altera GPIO IP core to ensure that the TimeQuest Timing

Analyzer analyzes the I/O timing correctly.

16

Timing Analysis

ug-altera_gpio

2014.08.18

Altera Corporation

Altera GPIO IP Core User Guide