10/100/1000 ethernet mac signals, Clock and reset signal, 10/100/1000 ethernet mac signals -2 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 117: And of, Are valid on the rising edge of, Description i/o name, Gm_tx_d[7:0], gm_tx_ en, gm_tx_err, M_tx_d[3:0, M_tx_en, M_tx_err

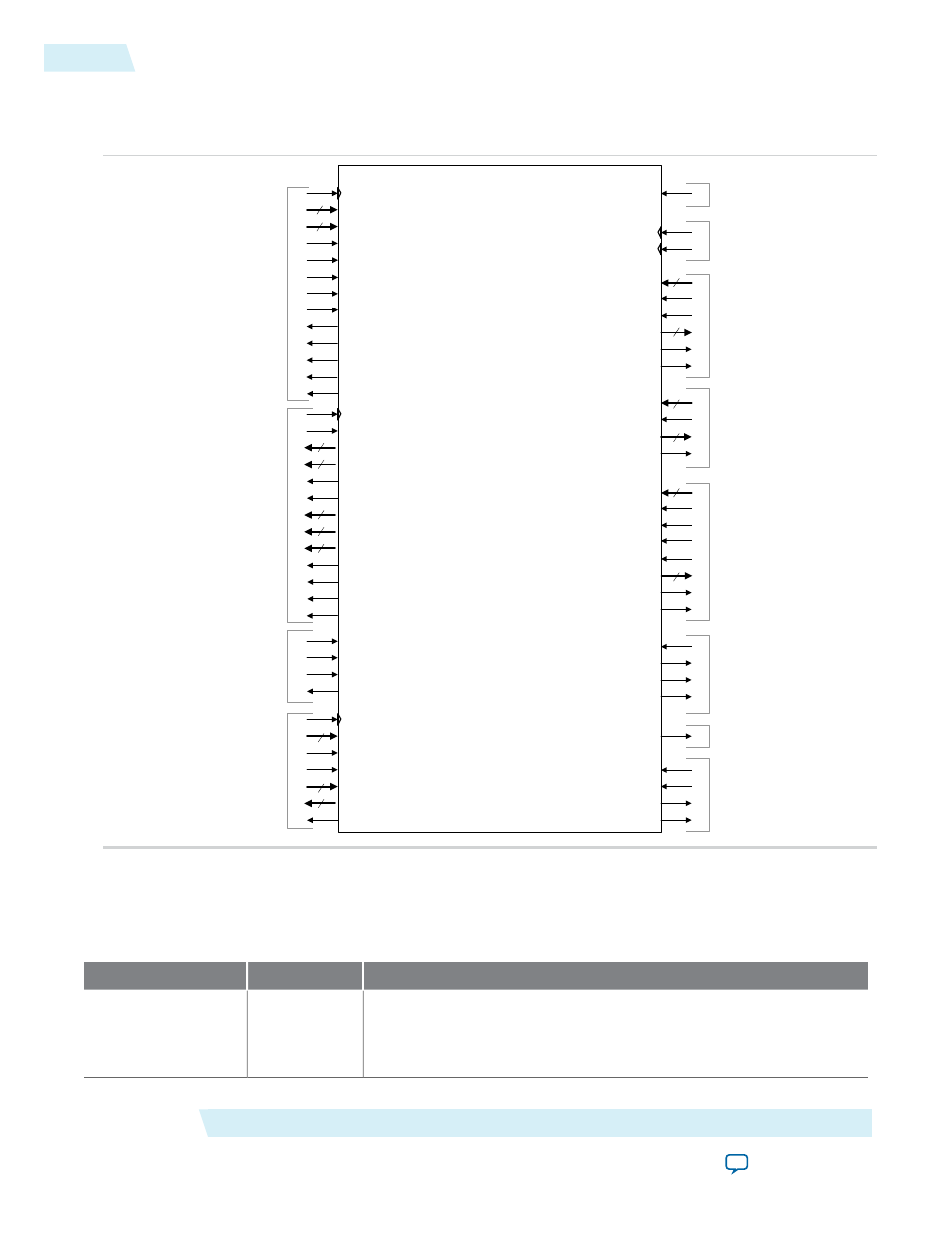

10/100/1000 Ethernet MAC Signals

Figure 7-1: 10/100/1000 Ethernet MAC Function with Internal FIFO Buffers Signals

10/100/1000 Ethernet MAC

PHY

Management

Signals

mdio_in

mdc

mdio_oen

mdio_out

Pause and Magic

Packet Signals

xon_gen

xoff_gen

magic_wakeup

magic_sleep_n

ff_rx_clk

MAC

Status

Signals

Clock

Signals

rx_clk

tx_clk

Reset

Signal

reset

n

2

MAC Transmit

Interface Signals

ff_tx_crc_fwd

ff_tx_data[DATAWIDTH-1:0]

ff_tx_eop

ff_tx_err

ff_tx_sop

ff_tx_wren

tx_ff_uflow

ff_tx_clk

ff_tx_rdy

ff_tx_septy

ff_tx_mod[1:0]

ff_tx_a_full

ff_tx_a_empty

2

n

6

18

4

MAC Receive

Interface Signals

ff_rx_data[DATAWIDTH-1:0]

ff_rx_mod[1:0]

ff_rx_eop

ff_rx_sop

rx_err[5:0]

rx_err_stat[17:0]

rx_frm_type[3:0]

ff_rx_dsav

ff_rx_rdy

ff_rx_dval

ff_rx_a_full

ff_rx_a_empty

32

32

MAC Control

Interface

Signals

clk

reg_addr[7:0]

reg_rd

reg_wr

reg_data_out[31:0]

reg_data_in[31:0]

reg_busy

8

4

4

MII

Signals

m_rx_d[3:0]

m_rx_en

m_rx_err

m_rx_col

m_rx_crs

m_tx_d[3:0]

m_tx_en

m_tx_err

8

GMII

Signals

gm_rx_d[7:0]

gm_rx_dv

gm_rx_err

gm_tx_d[7:0]

gm_tx_en

gm_tx_err

8

4

4

RGMII

Signals

rgmii_out[3:0]

tx_control

rgmii_in[3:0]

rx_control

ECC

Status

Signal

mac_eccstatus[1:0]

set_10_n

set_1000_n

ena_10_n

eth_mode_n

Clock and Reset Signal

Data transfers on the MAC Ethernet-side interface are synchronous to the receive and transmit clocks.

Table 7-1: GMII/RGMII/MII Clock Signal

Description

I/O

Name

GMII / RGMII/ MII transmit clock. Provides the timing reference for

all GMII / MII transmit signals. The values of

gm_tx_d[7:0], gm_tx_

en, gm_tx_err

, and of

m_tx_d[3:0]

,

m_tx_en

,

m_tx_err

are valid

on the rising edge of

tx_clk

.

I

tx_clk

Interface Signals

Altera Corporation

UG-01008

10/100/1000 Ethernet MAC Signals

7-2

2014.06.30