Altera Triple Speed Ethernet MegaCore Function User Manual

Page 220

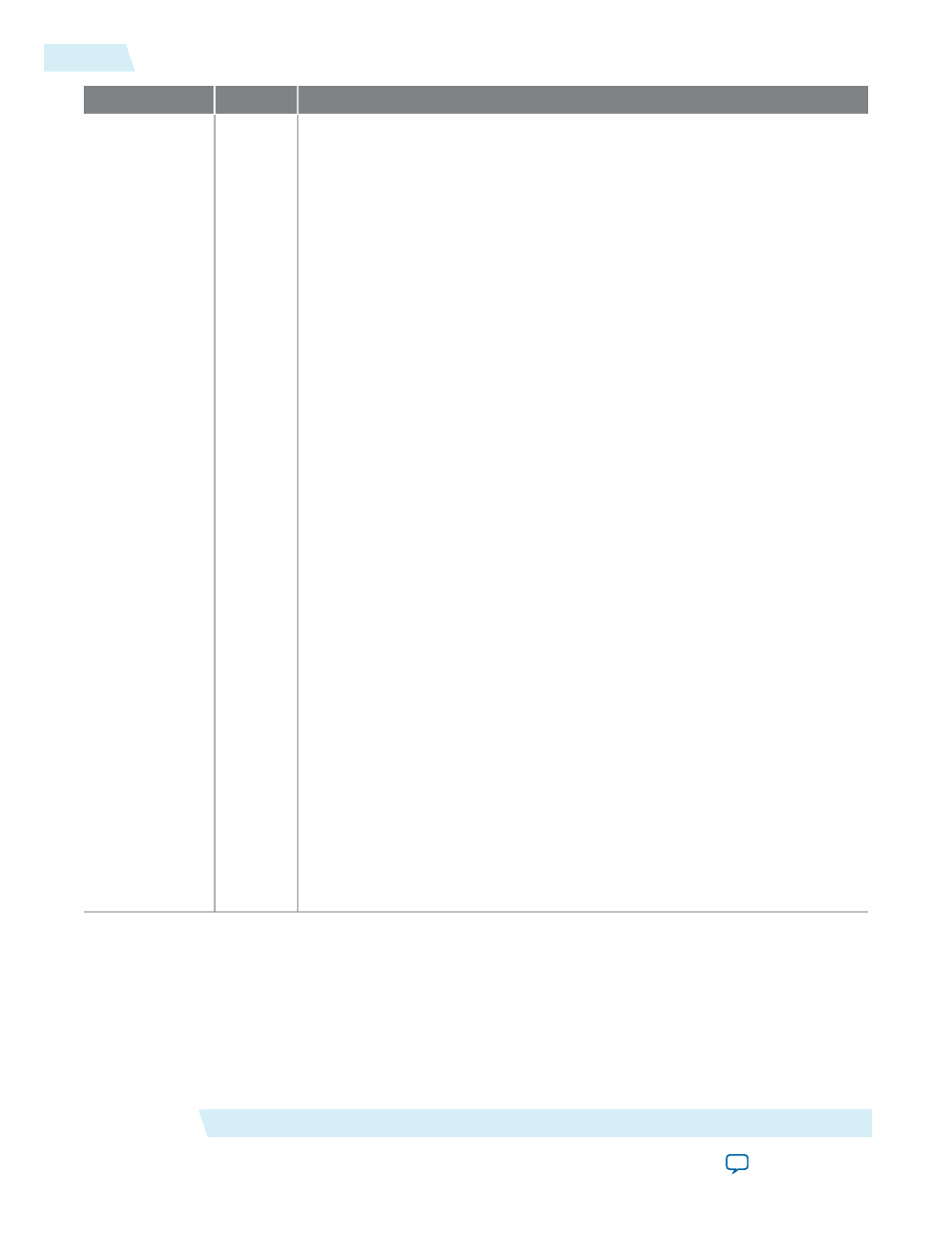

Changes

Version

Date

• Updated the MegaWizard Plug-In Manager flow in

Getting Started with

Altera IP Cores

.

• Added information about generating a design example and simulation

testbench in

Generating a Design Example or Simulation Model

on page

2-7.

• Updated the list of Quartus II generated files.

• Added information about the recommended pin assignments in

Constraint File No Longer Generated

on page 2-10.

• Updated the MegaCore parameter names and description in

Parameter

Settings

• Updated the IEEE 1588v2 feature list in

Functional Description

.

• Updated the SGMII auto-negotiation description in

Functional Description

.

• Added information about the IEEE 1588v2 feature PMA delay in

on page 6-17.

• Updated the Multiport Ethernet MAC with IEEE 1588v2, 1000BASE-X/

SGMII PCS and Embedded PMA Signals in

.

• Updated the IEEE 1588v2 timestamp signal names in

Interface Signals

.

• Added timing diagrams for IEEE 1588v2 timestamp signals in

Interface

Signals

.

• Added a section about migrating existing design to the Quartus II software

new MegaCore user interface in

Design Considerations

.

• Updated

Timing Constraints

chapter, to describe the new timing constraint

files and the recommended clock input frequency for each MegaCore Function

variant.

• Added information about the simulation model files generated using IEEE

simulation encryption in

on page 10-5.

• Updated the jumbo frames file directory in

on page

11-4.

• Updated the ToD configuration parameters in

on page 14-2 and ToD interface signals in

Figure D–1

,

on page 14-4 and

on page 14-3.

• Added information to describe the ToD’s drift adjustment in

on page 14-6.

• Added

ToD Synchronizer

and

Packet Classifier

chapters.

• Removed SOPC Builder information.

13.0

May 2013

Additional Information

Altera Corporation

UG-01008

Document Revision History

F-4

2014.06.30