1000base-x/sgmii pcs signals, 1000base-x/sgmii pcs signals -34 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 149

1000BASE-X/SGMII PCS Signals

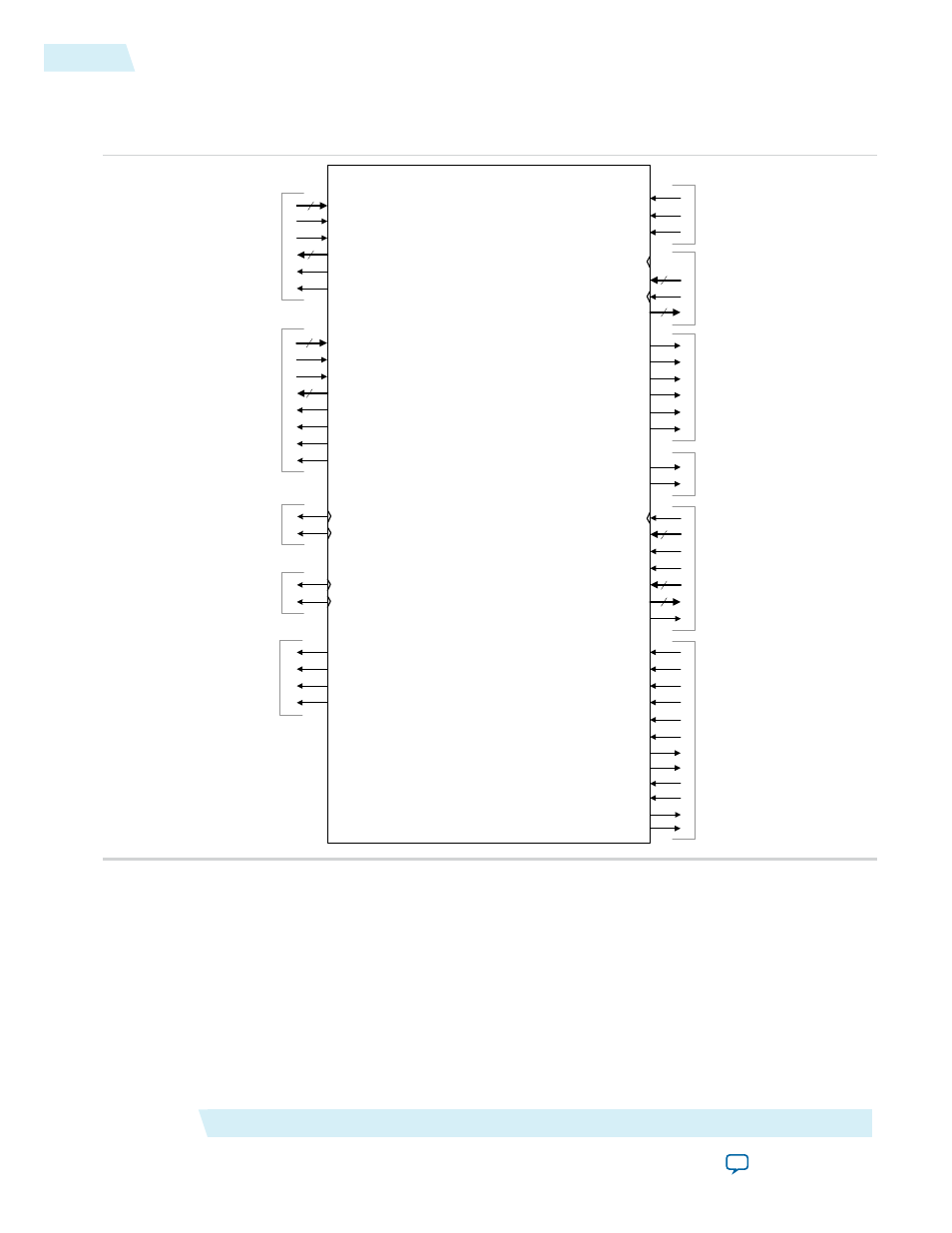

Figure 7-7: 1000BASE-X/SGMII PCS Function Signals

Reset

Signals

reset _rx _clk

reset _tx_clk

reset _reg _clk

set _10

set _100

set _1000

hd _ena

SGMII

Status

Signals

Status

LED

Signals

led _an

led _crs

led _col

led _char _err

led _link

led _disp _err

SERDES

Control

Signals

sd _loopback

powerdown

rx _clk

tx_clk

MII /GMII

Clock

Signals

rx _clkena

tx_clkena

Clock

Enabler

Signals

GMII

Signals

gmii _rx _d[7:0]

gmii _rx _dv

gmii _rx _err

gmii _tx_d[7:0]

gmii _tx_en

gmii _tx_err

8

8

mii_rx _d[3:0]

mii_rx _dv

mii_rx _err

mii_col

mii_crs

mii_tx_d[3:0]

mii_tx_en

mii_tx_err

MII

Signals

4

4

PCS

Control

Interface

Signals

reg _clk

reg _addr [4:0]

reg _rd

reg _wr

reg _data _out [15 :0]

reg _data _in[15 :0]

reg _busy

5

16

16

Ten Bit

Interface

Signals

tbi_rx _clk

tbi_rx _d[9:0]

tbi_tx_clk

tbi_tx_d[9:0]

10

10

Arria 10

Transceiver

Native PHY

Signals

1000 BASE-X/SGMII PCS Function

tx_serial_clk

rx_cdr_refclk

tx_analogreset

tx_digitalreset

rx_analogreset

rx_digitalreset

tx_cal_busy

rx_cal_busy

rx_set_locktodata

rx_set_locktoref

rx_is_locktodata

rx_is_locktoref

Note to

:

1. The clock enabler signals are present only in SGMII mode.

Interface Signals

Altera Corporation

UG-01008

1000BASE-X/SGMII PCS Signals

7-34

2014.06.30