Altera I/O Phase-Locked Loop (Altera IOPLL) IP Core User Manual

Page 2

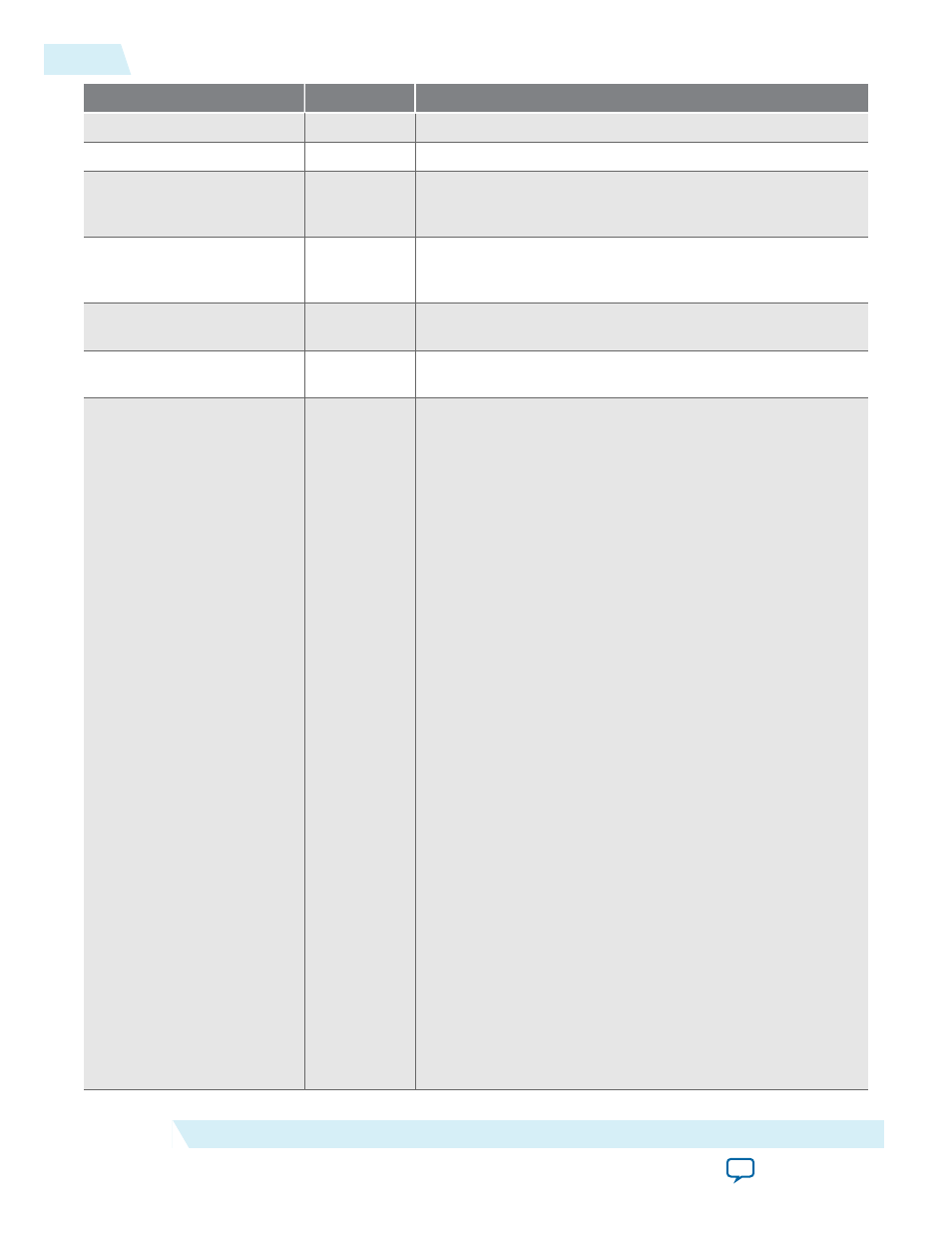

Parameter

Legal Value

Description

Component

—

Specifies the targeted device.

Speed Grade

—

Specifies the speed grade for targeted device.

PLL Mode

Integer-N PLL Specifies the mode used for the Altera IOPLL IP core. The

only legal selection is Integer-N PLL. If you need a fractional

PLL, you must use the Arria 10 FPLL IP core.

Reference Clock

Frequency

—

Specifies the input frequency for the input clock,

refclk

, in

MHz. The default value is 100.0 MHz. The minimum and

maximum value is dependent on the selected device.

Enable Locked Output

Port

Turn on or

Turn off

Turn on to enable the

locked

port.

Enable physical output

clock parameters

Turn on or

Turn off

Turn on to enter physical PLL counter parameters instead of

specifying a desired output clock frequency.

Operation Mode

direct,

external

feedback,

normal,

source

synchronous,

zero delay

buffer or lvds

Specifies the operation of the PLL. The default operation is

direct mode.

• If you select the direct mode, the PLL minimizes the

length of the feedback path to produce the smallest

possible jitter at the PLL output.The internal-clock and

external-clock outputs of the PLL are phase-shifted with

respect to the PLL clock input. In this mode, the PLL does

not compensate for any clock networks.

• If you select the normal mode, the PLL compensates for

the delay of the internal clock network used by the clock

output. If the PLL is also used to drive an external clock

output pin, a corresponding phase shift of the signal on

the output pin occurs.

• If you select the source synchronous mode, the clock

delay from pin to I/O input register matches the data

delay from pin to I/O input register.

• If you select the external feedback mode, you must

connect the

fbclk

input port to an input pin. A board-

level connection must connect both the input pin and

external clock output port,

fboutclk

. The

fbclk

port is

aligned with the input clock.

• If you select the zero delay buffer mode, the PLL must

feed an external clock output pin and compensate for the

delay introduced by that pin. The signal observed on the

pin is synchronized to the input clock. The PLL clock

output connects to the

altbidir

port and drives

zdbfbclk

as an output port. If the PLL also drives the

internal clock network, a corresponding phase shift of

that network occurs.

• If you select the lvds mode, the same data and clock

timing relationship of the pins at the internal SERDES

capture register is maintained. The mode compensates

for the delays in LVDS clock network, and between the

data pin and clock input pin to the SERDES capture

register paths.

2

Altera IOPLL IP Core Parameters - PLL Tab

UG-01155

2015.05.04

Altera Corporation

Altera I/O Phase-Locked Loop (Altera IOPLL) IP Core User Guide