Altera iopll ip core parameters - settings tab – Altera I/O Phase-Locked Loop (Altera IOPLL) IP Core User Manual

Page 4

Parameter

Legal Value

Description

Multiply Factor (M-

Counter)

(2)

4–511

Specifies the multiply factor of

M

-counter.

The legal range of the

M

counter is 4–511. However, restric‐

tions on the minimum legal PFD frequency and maximum

legal VCO frequency restrict the effective

M

counter range to

4–160.

Divide Factor (N-

Counter)

(2)

1–511

Specifies the divide factor of

N

-counter.

The legal range of the

N

counter is 1–511. However, restric‐

tions on the minimum legal PFD frequency restrict the

effective range of the

N

counter to 1–80.

Divide Factor (C-

Counter)

(2)

1-511

Specifies the divide factor for the output clock (

C

-counter).

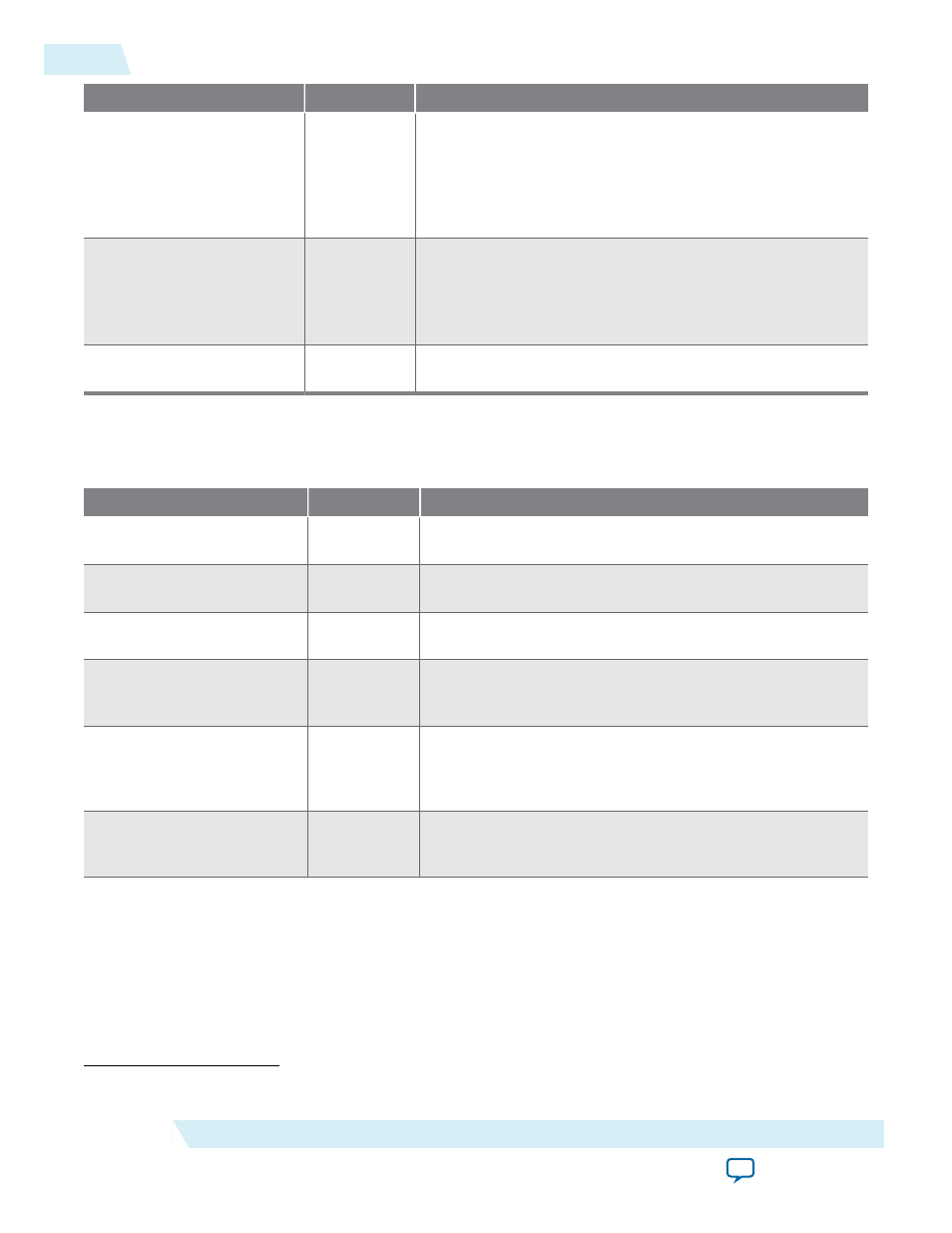

Altera IOPLL IP Core Parameters - Settings Tab

Table 2: Altera IOPLL IP Core Parameters - Settings Tab

Parameter

Legal Value

Description

PLL Bandwidth Preset

Low, Medium,

or High

Specifies the PLL bandwidth preset setting. The default

selection is Low.

PLL Auto Reset

Turn on or

Turn off

Automatically self-resets the PLL on loss of lock.

Create a second input clk

‘refclk1’

Turn on or

Turn off

Turn on to provide a backup clock attached to your PLL

that can switch with your original reference clock.

Second Reference Clock

Frequency

—

Selects the frequency of the second input clock signal. The

default value is 100.0 MHz. The minimum and maximum

value is dependent on the device used.

Create an ‘active_clk’ signal

to indicate the input clock

in use

Turn on or

Turn off

Turn on to create the

activeclk

output. The

activeclk

output indicates the input clock which is in use by the PLL.

Output signal low indicates

refclk

and output signal high

indicates

refclk1

.

Create a ‘clkbad’ signal for

each of the input clocks

Turn on or

Turn off

Turn on to create two

clkbad

outputs, one for each input

clock. Output signal low indicates the clock is working and

output signal high indicates the clock is not working.

(2)

This parameter is only available when Enable physical output clock parameters is turned on.

4

Altera IOPLL IP Core Parameters - Settings Tab

UG-01155

2015.05.04

Altera Corporation

Altera I/O Phase-Locked Loop (Altera IOPLL) IP Core User Guide