Logic, Figure 3–1 – Altera PowerPlay Early Power Estimator User Manual

Page 19

Altera Corporation

3–5

May 2008

PowerPlay Early Power Estimator For Arria GX FPGAs

Using the PowerPlay Early Power Estimator

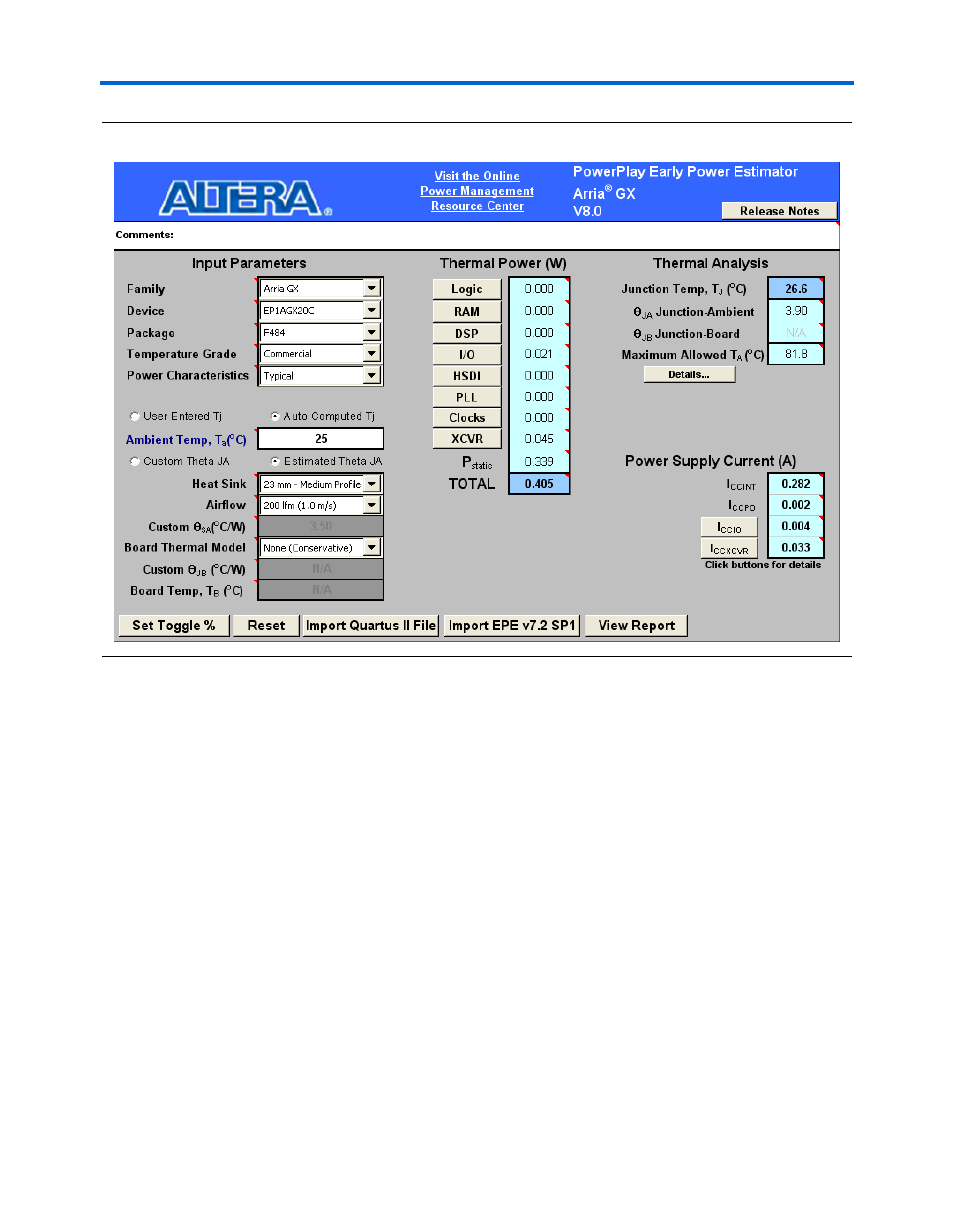

Figure 3–1. PowerPlay Early Power Estimator Spreadsheet Main Section

Logic

A design is a combination of several design modules operating at

different frequencies and toggle rates. Each design module can have a

different amount of logic. For the most accurate power estimation,

partition the design into different design modules. You can partition your

design by grouping modules by clock frequency, location, hierarchy, or

entities.

Each row in the Logic section represents a separate design module. You

must enter the following parameters for each design module

■

Clock frequency (f

MAX

) in MHz

■

Number of combinational adaptive look-up tables (ALUTs)

■

Number of registers

■

Toggle percentage