Appendix a: watchdog timer – NEXCOM NDiS 126 User Manual

Page 75

Advertising

Copyright © 2011 NEXCOM International Co., Ltd. All Rights Reserved.

87

NDiS 126 User Manual

Appendix A: Watchdog Timer

Appendix A: Watchdog Timer

NDiS 126 features a watchdog timer that resets the CPU or generates

an interrupt if the processor stops operating for any reason. This

feature ensures system reliability in industrial standalone or unmanned

environments.

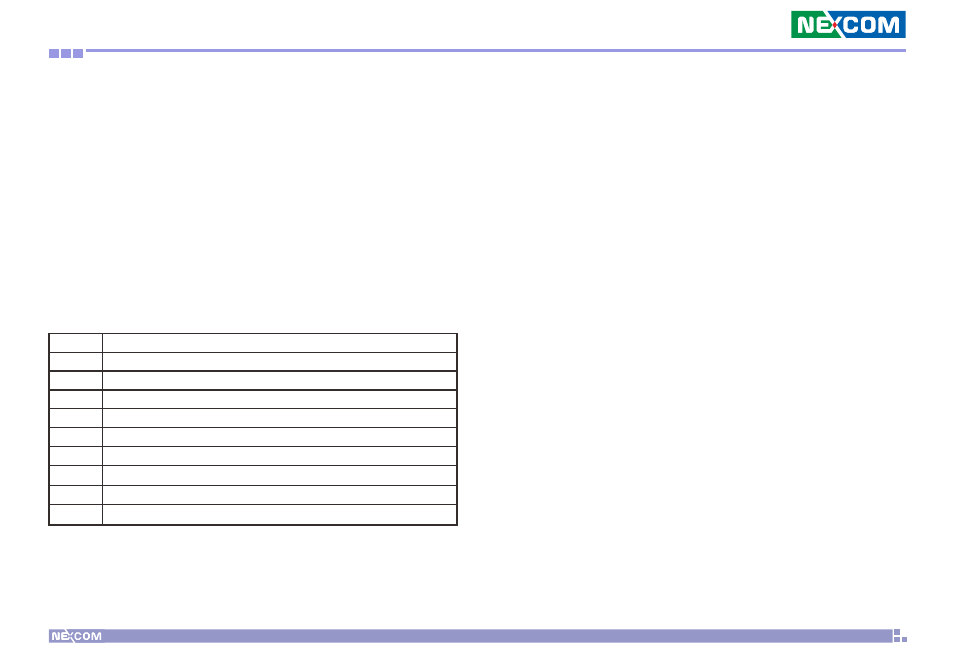

Watchdog Timer Control Register

(Index=71h, Default=00h)

Bit

Description

7

WDT is reset upon a CIR interrupt.

6

WDT is reset upon a KBC (mouse) interrupt.

5

WDT is reset upon a KBC (keyboard) interrupt.

4

WDT is reset upon a read or a write to the Game Port base address.

3-2

Reserved

1

Force Time-out. This bit is self-clearing.

WDT Status

0

1: WDT value reaches 0.

0: WDT value is not 0.

Advertising