Power supervisor real-time clock, D0} /{d1, I2c bus address – Zilog EZ80190 User Manual

Page 75

Advertising

UM014108-0810

Schematic Diagrams

eZ80190 Development Kit

User Manual

71

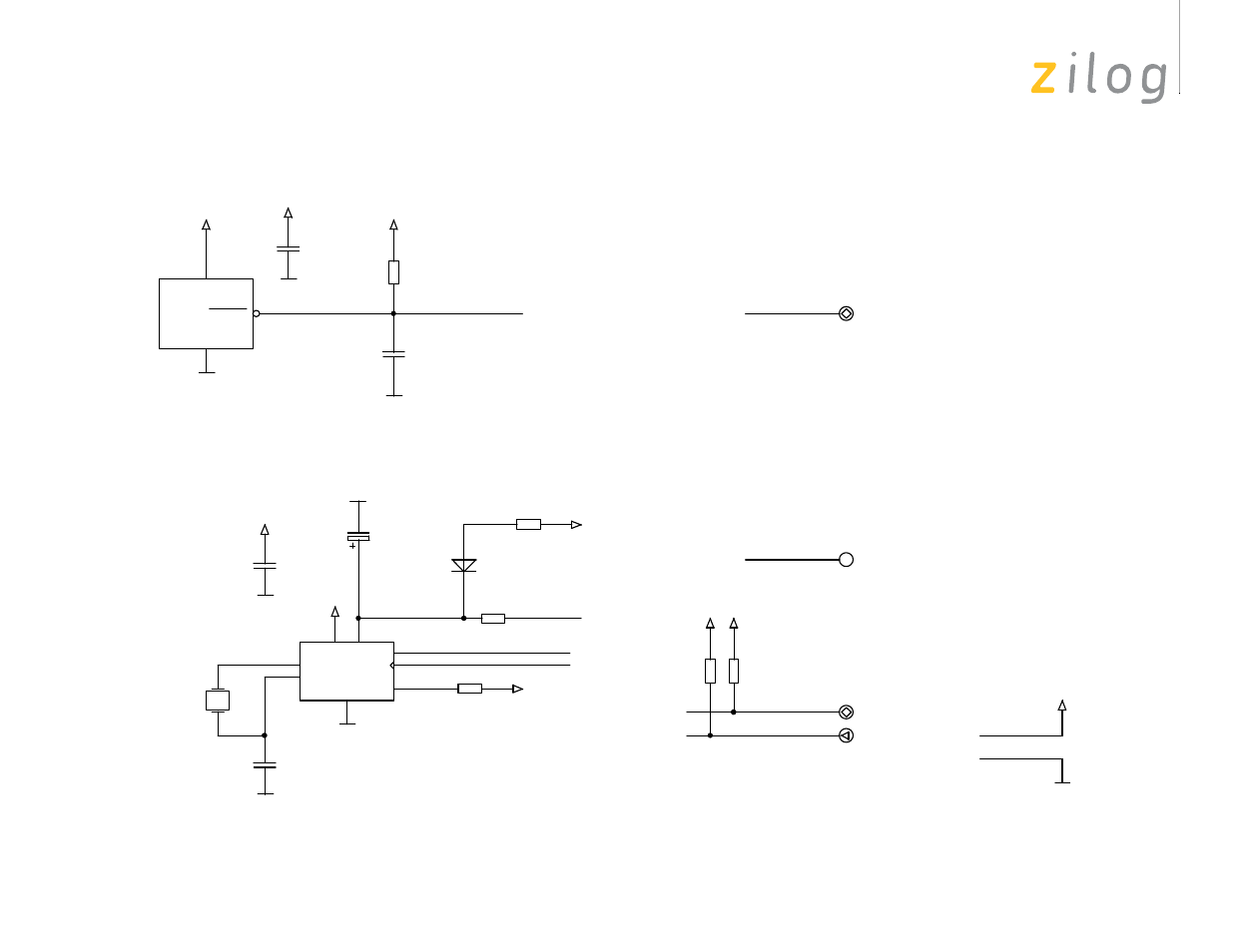

Figure 26. eZ80190 Module Schematic Diagram, #6 of 8—Ethernet Module Peripherals

open-drain

{D0} /{D1}

H

H

-R ESET

-R ESET

VSS

VD D

IIC SD A

II

CS CL

IIC SD A

II

CS CL

VBAT

RTC _VD D

RTC _VD D

IIC SD A

II

CS CL

RTC _VD D

-R ESET

V3.3

V3.3

GND

V3.3

R20

0R

0603

R 18

2k2

0603

C 7

100nF

0603

C8

10nF

0603

R 23

4k7

0603

U12

M AX6328UR29

SO T-23-L3

2

1

3

RESET

GND

VDD

C 10

100nF

0603

U 13

M 41T11M 6

SO 8.150

1

2

4

8

7

6

5

3

O SC I

OS CO

GND

V+

FT/OUT

SCL

SD A

VBA

T

C11

unpl

ace

0603

Y2

32.7

68kH z

XTAL3

R 22

4k7

0603

R21

4k7

0603

D 1

TM M

BAT

41

M IN IM ELF_AK

R19

100

0603

power supervisor

real-time clock

alternative:

Maxim MAX6802UR29D3

Gold Cap

C9

0,1F

GOLDCAP_SD_V

I2C bus address:

Advertising