0x0152:0x0153 – BECKHOFF EtherCAT Registers Section II User Manual

Page 45

PDI Configuration (0x0150:0x0153)

Slave Controller

– Register Description

II-33

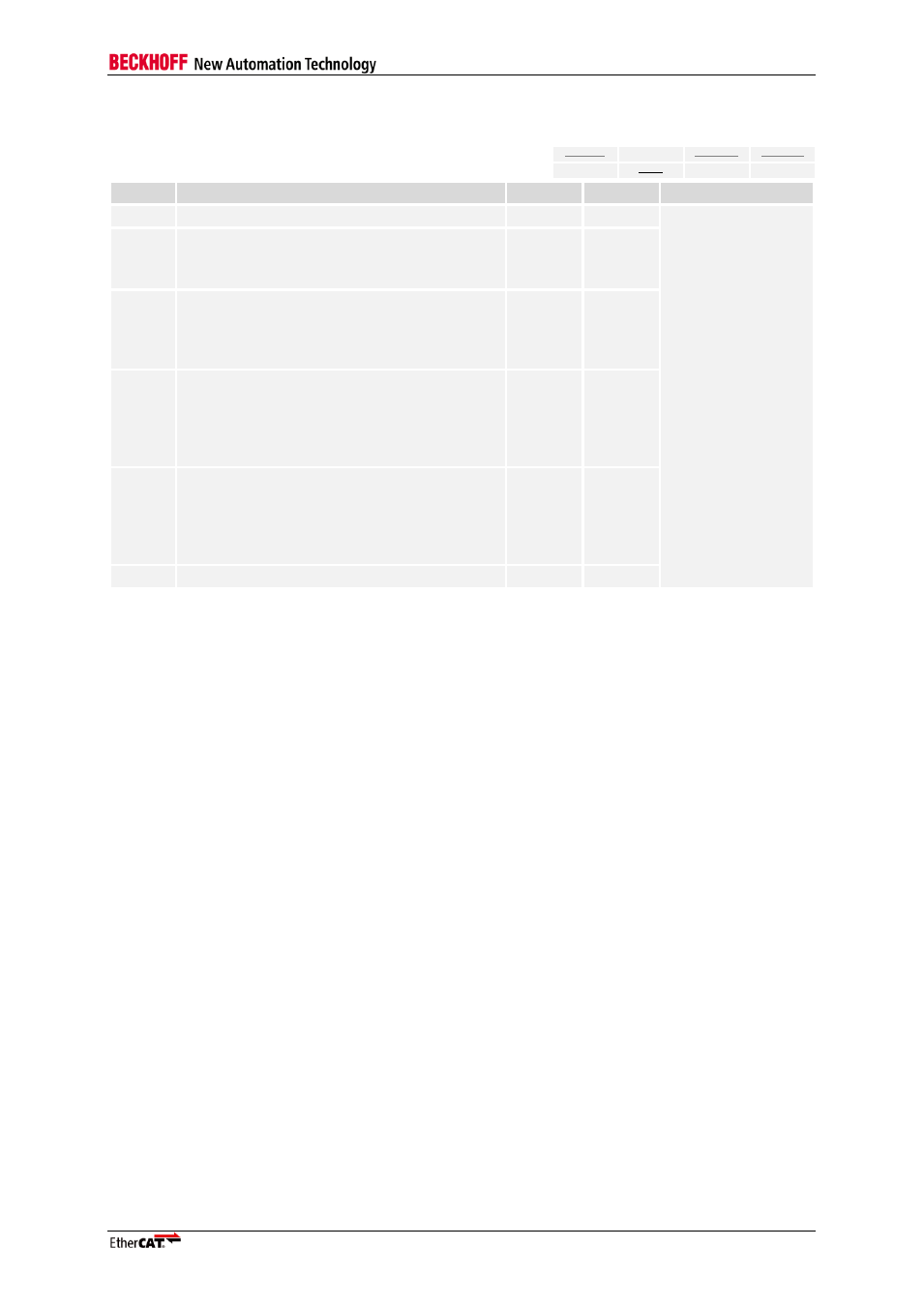

Table 40: Register PDI Synchronous Microcontroller extended Configuration (0x0152:0x0153)

ESC20

ET1100

ET1200

IP Core

[7:0]

Bit

Description

ECAT

PDI

Reset Value

7:0

Reserved, set EEPROM value 0

r/-

r/-

0, later EEPROM ADR

0x0003

8

Write data valid:

0:

Write data valid one clock cycle after CS

1:

Write data valid together with CS

r/-

r/-

9

Read mode:

0:

Use Byte Selects for read accesses

1:

Ignore Byte Selects for read accesses,

always read full PDI width

r/-

r/-

10

CS mode:

0:

Sample CS with rising edge of

CPU_CLK

1:

Sample CS with falling edge of

CPU_CLK

r/-

r/-

11

TA/IRQ mode:

0:

Update TA/IRQ with rising edge of

CPU_CLK

1:

Update TA/IRQ with falling edge of

CPU_CLK

r/-

r/-

15:12

Reserved, set EEPROM value 0

r/-

r/-