Dds register 5 – step increment msb - 0x25 – Sundance SMT350 User Manual

Page 39

Version 1.9

Page 39 of 45

SMT350 User Manual

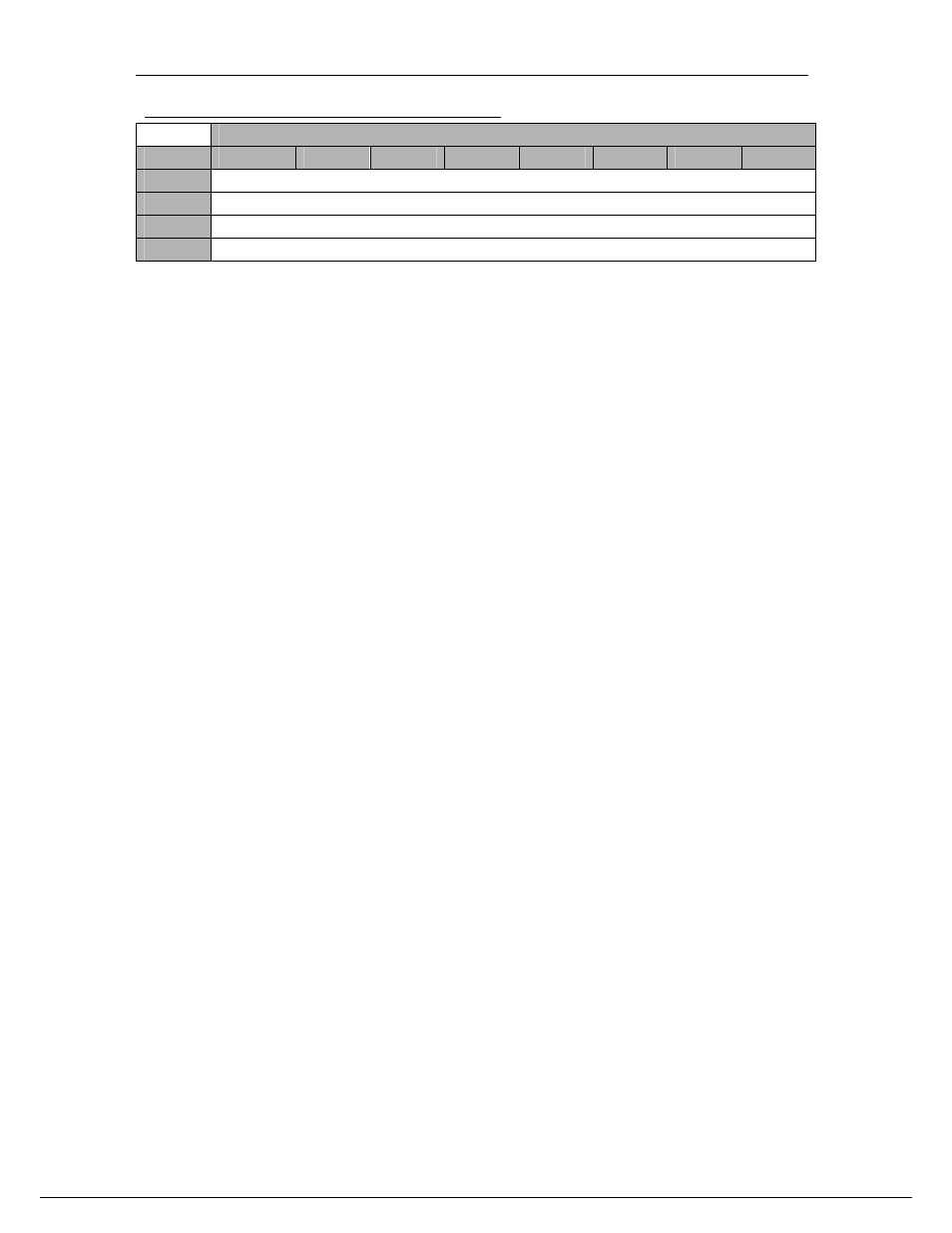

DDS Register 5 – Step Increment MSB - 0x25

DDS Register 5 – 0x25

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

DDS Step Phase Increment [31…24]

Default

‘00000000’

0

DDS Step Phase Increment [23…16]

Default

‘00000000’

The Step Phase Increment value is coded on 32 bits. It corresponds to the increment

in phase on each sampling clock cycle (Sweep Mode).

When used to generate a fixed frequency, Start Phase Increment should be equal

to Stop Phase Increment and Step Phase Increment should be equal to 1.

For Registers 0x24 and 0x25 to take effect, Bit 6 of register 0x1D must be set to 1.

DAC Channel A is the Sine output of the DDS and DAC Channel B is the Cosine

output of the DDS. Both outputs are therefore is quadrature.