Jp2- ttl i/o, Shb pin-out – Sundance SMT395E User Manual

Page 27

Version 2.1

Page 27 of 30

SMT395Q User Manual

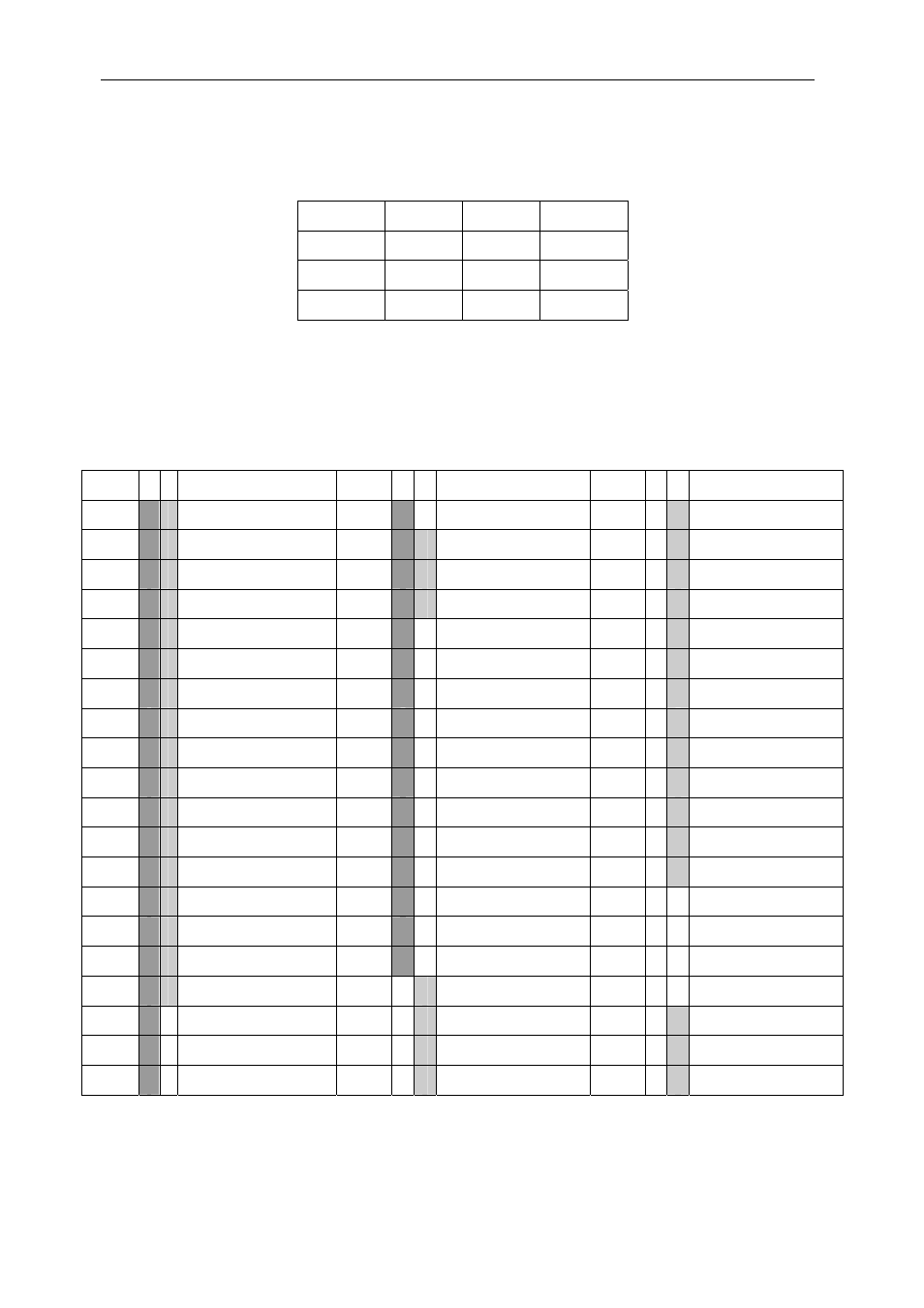

JP2- TTL I/O

This table shows the pin-out and organisation of the TTL I/O header.

Signal Pin Pin Signal

GND 6 3 TTL1

TTL3 5 2 TTL0

TTL2 4 1 3.3V

These pins are directly connected to the FPGA and can be used as either input or output of

LVTTL (3.3V) signals. Useful for test/probe points.

SHB pin-out

Pin

Signal

Pin

Signal

Pin

Signal

1

CLK0 21

D19

41 D39

2

D0 22

D20/

WEN1 42

D40

3

D1 23

D21/

REQ1 43

D41

4

D2 24

D22/

ACK1 44

D42

5

D3 25

D23/

CLK2

45 D43

6

D4 26

D24

46 D44/

WEN3

7

D5 27

D25

47 D45

REQ23

8

D6 28

D26

48 D46/

ACQ3

9

D7 29

D27

49 D47/

CLK3

10

D8/

WEN0 30

D28

50 D48

11

D9/

REQ0 31

D29

51 D49

12

D10/

ACK0 32

D30

52 D50

13

D11/CLK1 33

D31

53 D51

14

D12 34

D32/WEN2

54

D52

15

D13 35

D33/REQ2

55

D53

16

D14 36

D34/

ACK2

56

D54

17

D15 37

D35/

CLK3 57

D55

18

D16

38 D36 58

D56/

WEN4

19

D17

39 D37 59

D57/

REQ4

20

D18

40 D38 60

D58/

ACK4