Altera MAX 10 JTAG User Manual

Page 10

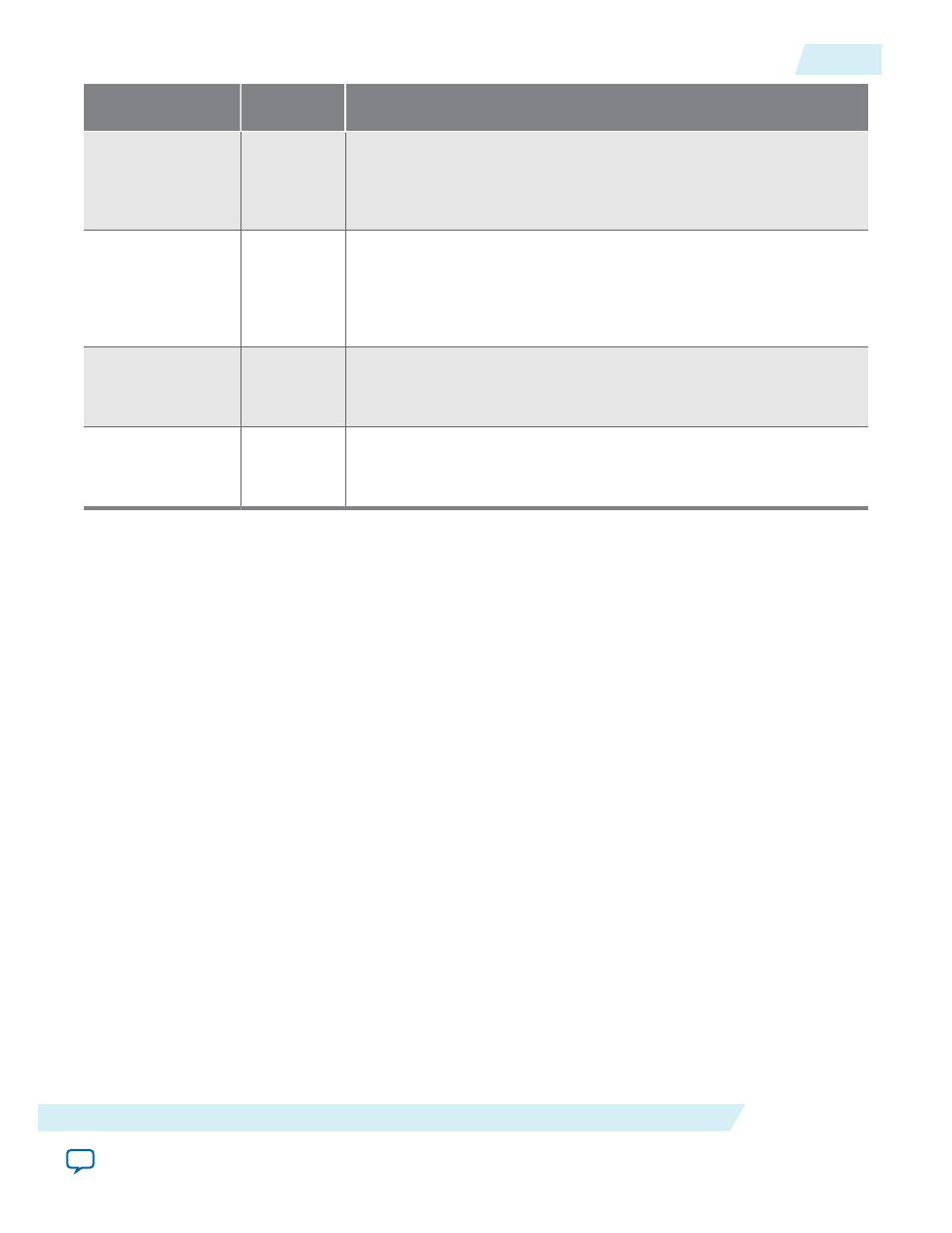

Instruction Name

Instruction

Binary

Description

HIGHZ

(1)

00 0000 1011 • Places the 1-bit bypass register between the

TDI

and

TDO

pins. The

1-bit bypass register tri-states all the I/O pins.

• Allow the BST data to pass synchronously through target devices to

adjacent devices if device is operating in normal mode.

CLAMP

(1)

00 0000 1010 • Places the 1-bit bypass register between the

TDI

and

TDO

pins. The

1-bit bypass register holds I/O pins to a state defined by the data in

the boundary-scan register.

• Allow the BST data to pass synchronously through target devices to

adjacent devices if device is operating in normal mode.

USER0

00 0000 1100 • Allows you to define the scan chain between the

TDI

and

TDO

pins

in the MAX 10 logic array.

• Use this instruction for custom logic and JTAG interfaces.

USER1

00 0000 1110 • Allows you to define the scan chain between the

TDI

and

TDO

pins

in the MAX 10 logic array.

• Use this instruction for custom logic and JTAG interfaces.

UG-M10JTAG

2015.05.04

JTAG Instructions

3-3

JTAG BST Operation Control

Altera Corporation