Jtag secure mode, Jtag private instruction, Jtag instructions – Altera MAX 10 JTAG User Manual

Page 9: Jtag secure mode -2, Jtag private instruction -2, Jtag instructions -2

JTAG Secure Mode

In JTAG secure mode, the device only allow

SAMPLE/PRELOAD

,

BYPASS

,

EXTEST

, and

IDCODE

JTAG

instructions.

Related Information

Provides more information about the JTAG Secure Mode.

JTAG Private instruction

Caution:

Never invoke the following instruction codes. These instructions can damage the device and

render it unusable:

• 10 0100 0000

• 10 0011 0000

• 10 1110 0000

• 10 0011 0001

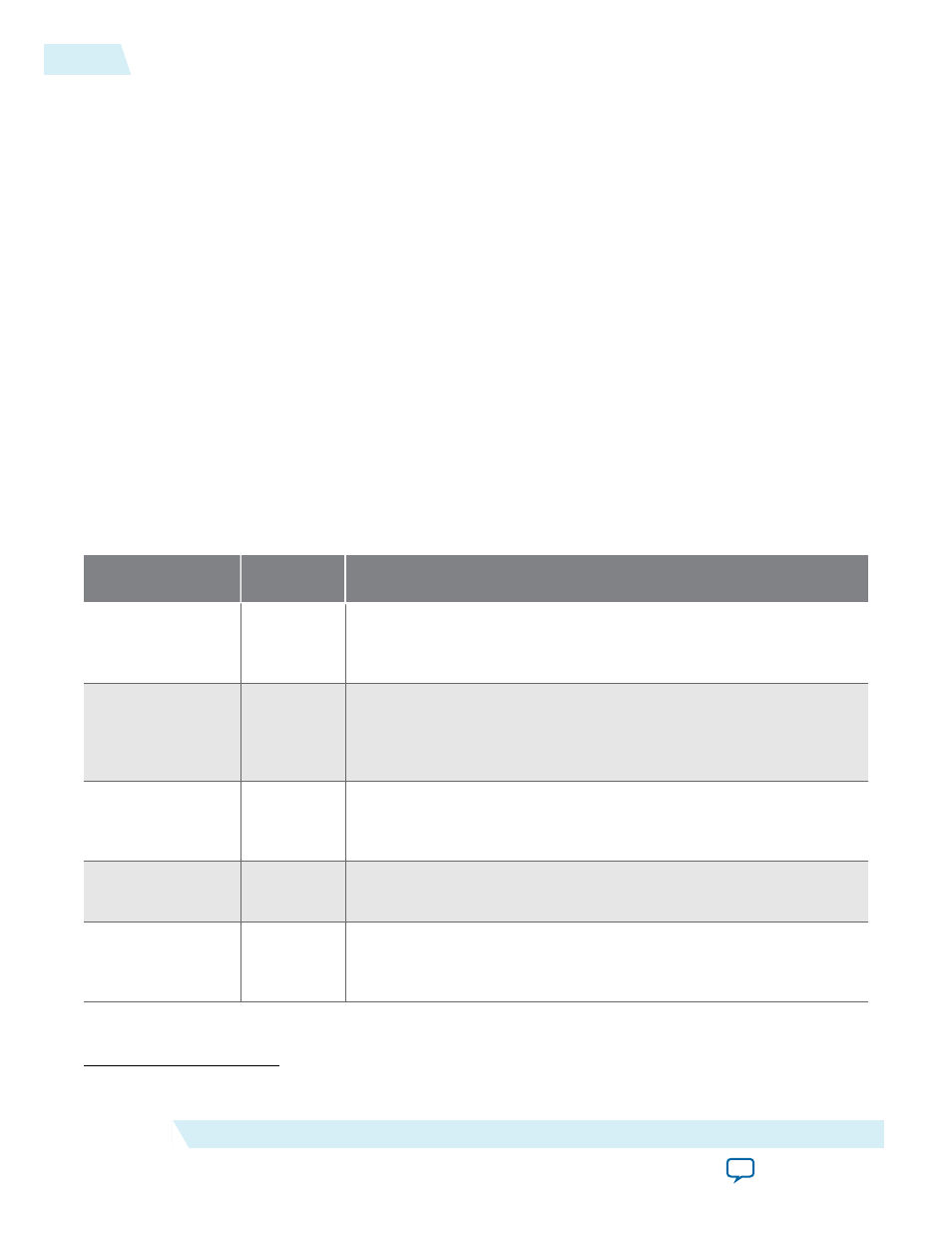

JTAG Instructions

Instruction Name

Instruction

Binary

Description

SAMPLE/PRELOAD

00 0000 0101 • Permits an initial data pattern to be an output at the device pins.

• Allows you to capture and examine a snapshot of signals at the

device pins if the device is operating in normal mode.

EXTEST

(1)

00 0000 1111 • Forces test pattern at the output pins and capture the test results at

the input pins.

• Allows you to test the external circuitry and board-level intercon‐

nects.

BYPASS

11 1111 1111 • Places the 1-bit bypass register between the

TDI

and

TDO

pins.

• Allows the BST data to pass synchronously through target devices

to adjacent devices during normal device operation.

USERCODE

00 0000 0111 • Places the 1-bit bypass register between the

TDI

and

TDO

pins.

• Allows you to shift the

USERCODE

register out of the

TDO

pin serially.

IDCODE

00 0000 0110 • Selects the

IDCODE

register and places it between the

TDI

and

TDO

pins.

• Allows you to shift the

IDCODE

register out of the

TDO

pin serially.

(1)

HIGHZ

,

CLAMP

, and

EXTEST

instructions do not disable weak pull-up resistors or bus hold features.

3-2

JTAG Secure Mode

UG-M10JTAG

2015.05.04

Altera Corporation

JTAG BST Operation Control